# Readout Electronics for Low Dark Count Geiger Mode Avalanche Photodiodes Fabricated in Conventional HV-CMOS Technologies for Future Linear Colliders

<u>E. Vilella<sup>1</sup></u>, A. Arbat<sup>1</sup>, J. Trenado<sup>2</sup>, O. Alonso<sup>1</sup>, A. Comerma<sup>2</sup>, D. Gascon<sup>2</sup>, A. Vilà<sup>1</sup>, L. Garrido<sup>2</sup>, A. Diéguez<sup>1</sup>

<sup>1</sup>Systems Instrumentation and Communications (SIC) – Dept. of Electronics <sup>2</sup>Dept. of Structure and Constituents of Matter University of Barcelona (UB), Barcelona, Spain <u>evilella@el.ub.es</u>

- o Introduction

- Avalanche photodiodes in CMOS

- o Technologies under comparison

- GAPDs and readout circuits for HEP experiments

- Beam structure

- Proposed readout circuits

- Test and results

- Comparison

- o Conclusions

Outline

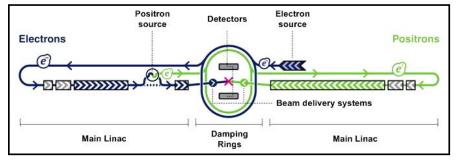

#### **Motivation: Future colliders**

- ✓ Next collider will be a linear collider

- ✓ Still not clear whether a ~ 1TeV (ILC) or multi TeV (~3TeV) CLIC

- Strict technology requirements posed

by the ILD (International Large Detector)

Concept Group (last version Feb. 2010)

- Low material budget (0.2-0.5% X<sub>0</sub>)

- To reduce errors from multiple scattering

- High spatial resolution

UNIVERSITAT DE BARCELONA

- Best achievable  $\Phi$  resolution  $\rightarrow$  5µm

- Pixel size  $\rightarrow$  20µm x 100µm

- Occupancy (3rd layer of the FTD)

- Background level  $\rightarrow$  0.001-0.002 hits/cm<sup>2</sup>/BX

- High readout speed

- BX ILC  $\rightarrow$  337 ns

- BX CLIC  $\rightarrow$  0.5 ns

- Radiaton tolerance & EMIs tolerance

- Minimum power dissipation (no cooling)

POSTBON CONTRACTOR MINIMATERI VICTORIAL MINIMATERI VICTORIAL

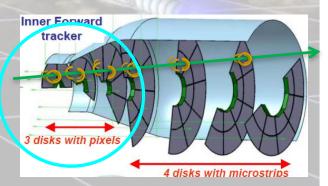

#### **Vertex detector**

#### **Tracker detector**

ICCU

Department

Universitat de Barcelona

UNIVERSITAT DE BARCELONA

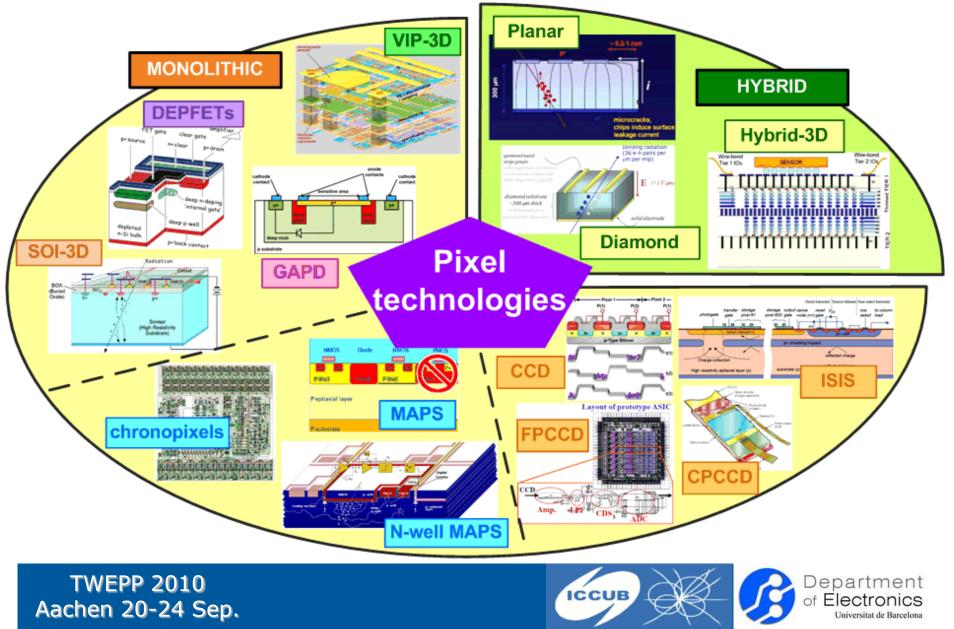

#### Pixel detectors

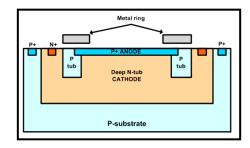

## Avalanche photodiodes in CMOS (1)

CCU

TWEPP 2010 Aachen 20-24 Sep.

Department

Universitat de Barcelona

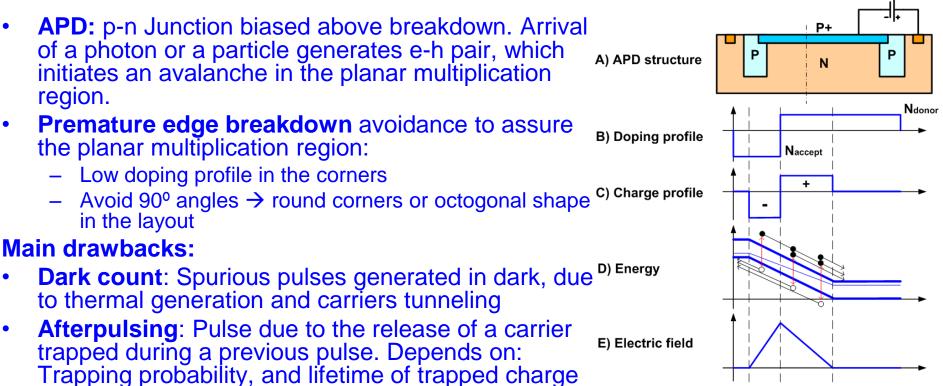

#### • Motivation for Geiger-mode APDs

- ☑ A detector with high intrinsic gain (>10<sup>8</sup>)

- ☑ Excellent timing accuracy

- ps rise time

- short recovery times

- possible single hit detection

- ☑ Compatible with standard CMOS technologies

- on-chip integration of readout circuits

- low supply voltage requirements

- reduced power consumption

## • However...

- High intrinsic level of noise (dark counts)

- false counts

- severe performance limitation

- increase of the readout electronics area to store the false hits

B

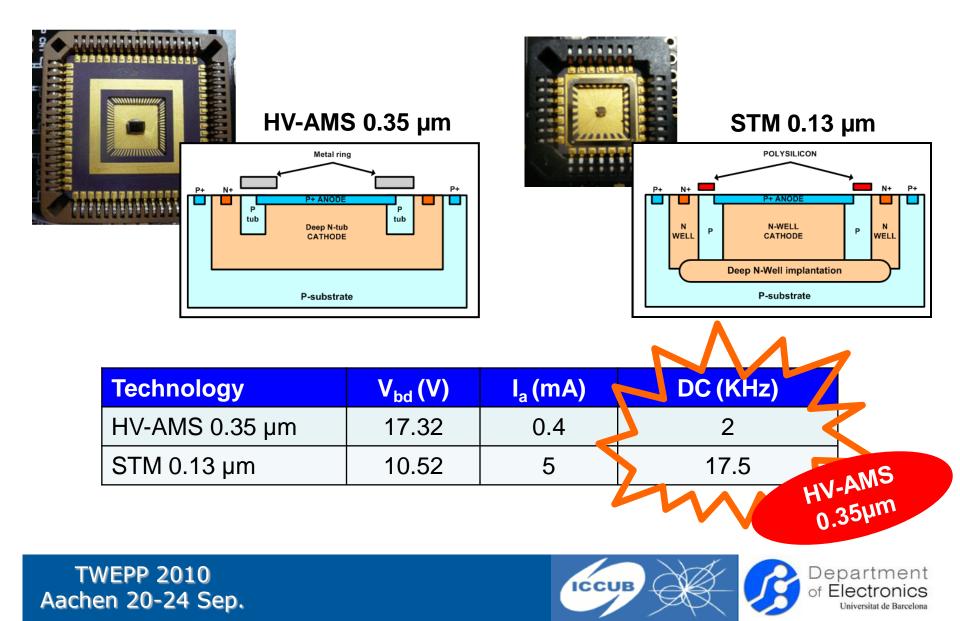

#### **Technologies under comparison**

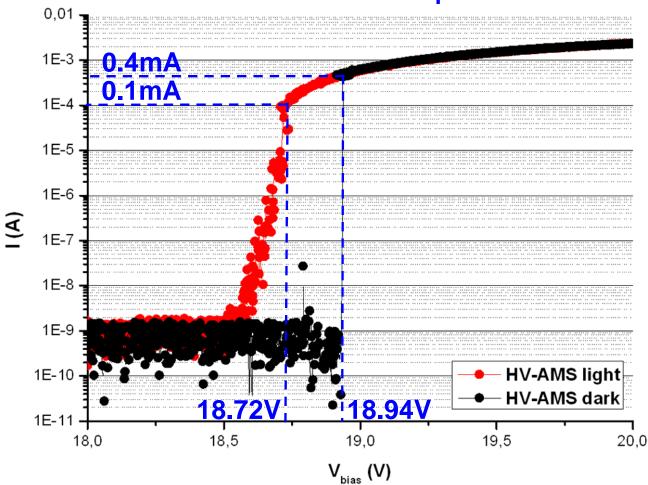

#### **Characterization:** V<sub>BD</sub> & linear mode

Department

Electronics

Universitat de Barcelona

#### 2010 APDs chip

ICCUB

#### **Beam structure**

0.114

$\boxtimes$

0.1

0.2

HV 0.35um 20x20 LV 0.13um 20x20

HV 0.35um 20x100

30.28

17.36

2.06k

0.4

Department

Electronics

Universitat de Barcelona

0.5

0.6

35.0k

30.0k

25.0k

20.0k

15.0k

10.0k

5.0k

counts/s

ICCU

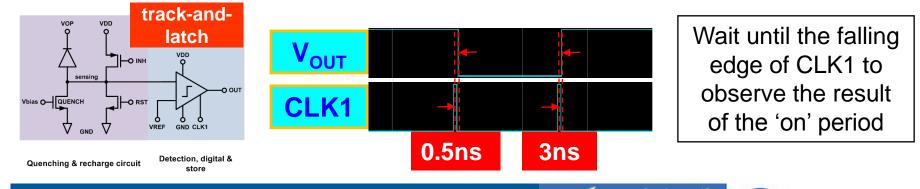

acquisition phase

readout phase

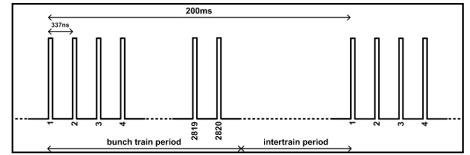

- $\circ$  ILC timing

- 2820 BX in 0.95ms

- BX spacing of 337ns

- 199.05ms quiet time

#### • ILC background

• 0.001-0.003 hits/cm<sup>2</sup>/BX for the 3<sup>rd</sup> layer of the FTD

$(0.003 \text{ hits/cm}^2/BX) \cdot \frac{1 \text{ cm}^2}{(1 \cdot 10^4 \, \mu \text{ m})^2} \cdot \frac{20 \, \mu \text{ mx} 100 \, \mu \text{ m}}{\text{ pixel}} \cdot \frac{2820 \, \text{BX}}{\text{ train}} = 1.69 \cdot 10^{-16} \, \text{hits/ pixel/train}$

#### $\circ$ ~ 0.35 $\mu m$ HV-AMS CMOS DC noise in ILC

38kHz/pixel (20µm x 100µm @ 18.28V)

$D.C._{EFFECTIVE} = \frac{38kHz}{pixel} \cdot 10ns \cdot \frac{2820BX}{train} = 1 \ false \ hits/ \ pixel/train$

Gated acquisition

0.3

Overvoltage (V)

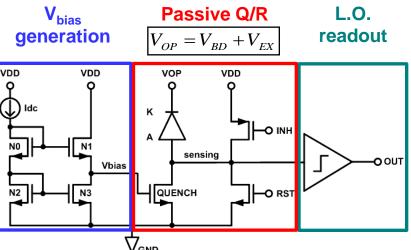

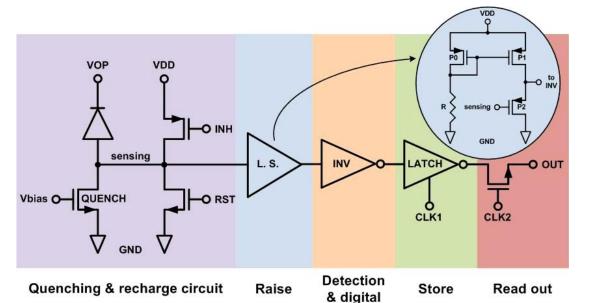

## **Readout circuits.** V<sub>bias</sub> generation.

#### **V**<sub>bias</sub> generation 0

- Current source  $\rightarrow$  control of  $\Delta V_{\text{sensing}}$  during the 'off' period thanks to  $I_{\text{DC}} \rightarrow \left| \Delta V_{\text{sensing}} = (\tau_{OFF}/C) \cdot I_{DC} \right|$

- Traps emptied before the new 'on' period  $\rightarrow$  afterpulsing probability  $\downarrow$

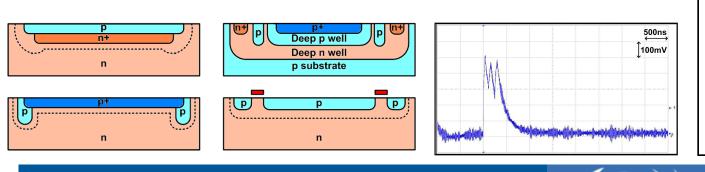

#### Passive quenching/recharge Ο

- **QUENCH** Active load  $\rightarrow$  pMOS or nMOS topology?

- nMOS topology allows fully isolation between the deep ntub/p-substrate and the sensing node  $\rightarrow$  reduction of the total capacitance  $\rightarrow$  response time  $\downarrow$

- nMOS transistor with  $(W/L)_{n} = (0.8 \mu m/5 \mu m)$

- $I_D < I_{GAPD}$  latching current  $\rightarrow$  correct quenching

- **INH** Gate command through pMOS transistor.

- $INH = 1^{\circ} \rightarrow 0^{\circ} \text{ period} \rightarrow \text{free running}$

- INH = '0'  $\rightarrow$  'off' period  $\rightarrow$  no particle detection

- **RST** GAPD recharge through nMOS transistor.

- RST = '1'  $\rightarrow$  V<sub>OP</sub> is restored (1ns)

#### L.O. readout... $\bigcirc$

but V<sub>Th</sub> of MOS transistors (V<sub>Thp</sub>=0.65V, V<sub>Thn</sub>=0.5V) makes avalanche detection difficult...

ICCUB

**TWEPP 2010** Aachen 20-24 Sep.

Department

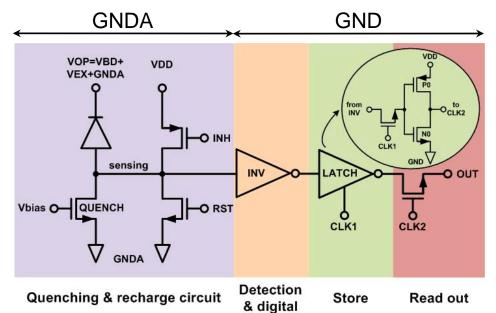

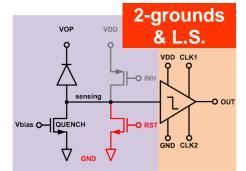

#### Readout circuits. 2 grounds scheme.

| Gated acquisition                       | CLK1       | INH |  |

|-----------------------------------------|------------|-----|--|

| 'on' period                             | <b>'1'</b> | '1' |  |

| 'off' period                            | '0'        | '0' |  |

| Reset → RST = '1'                       |            |     |  |

| <b>Readout</b> $\rightarrow$ CLK2 = '1' |            |     |  |

#### Main features:

- 2nd ground (GNDA > GND) to enable low V<sub>EX</sub> operation

- Minimum area latch to store the resulting value of the 'on' period

- Readout with external control (CLK2 pass gate)

- Upon particle hit (or D.C):

An avalanche fires

V increases from

- $V_{sensing}$  increases from GNDA  $\rightarrow$  GNDA+ $V_{EX}$

- If GNDA+V<sub>EX</sub> > V<sub>th</sub> inverter

→ the avalanche is detected

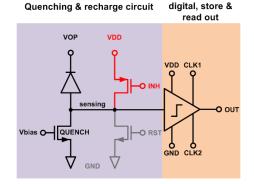

#### Readout circuits. Level shifter.

#### Main features:

- L.S. with external resistor

- Minimum area latch to store the resulting value of the 'on' period

- Readout with external control (CLK2 pass gate)

| Gated acquisition                       | CLK1       | INH |  |

|-----------------------------------------|------------|-----|--|

| 'on' period                             | <b>'1'</b> | '1' |  |

| 'off' period                            | '0'        | '0' |  |

| Reset → RST = '1'                       |            |     |  |

| <b>Readout</b> $\rightarrow$ CLK2 = '1' |            |     |  |

- <u>Upon particle hit (or D.C):</u>

- An avalanche fires

- +  $V_{\text{sensing}}$  increases from  $\text{GND} \rightarrow \text{V}_{\text{EX}}$

- L.S. raises V<sub>EX</sub> to V<sub>EX</sub> > V<sub>th</sub> inverter (1.65V)

→ the avalanche is detected

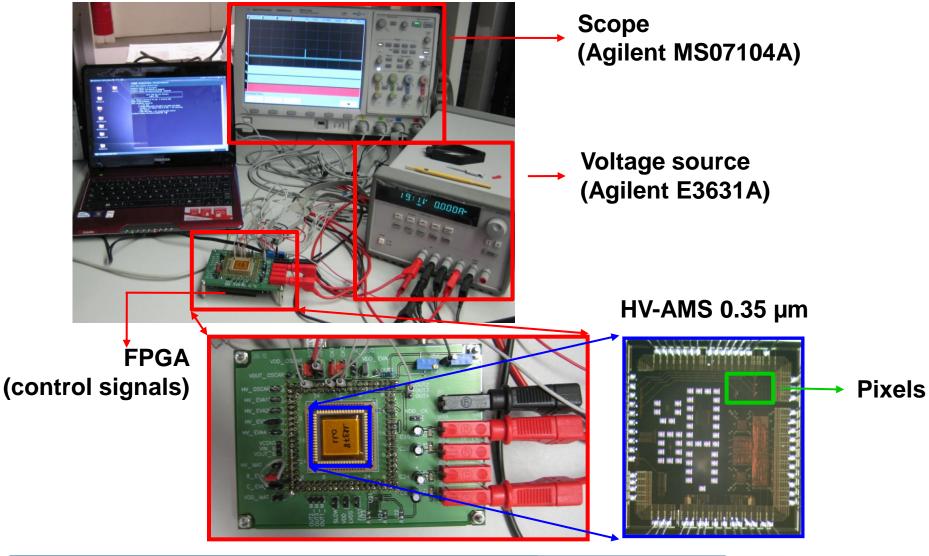

#### Test. Set-up.

UNIVERSITAT DE BARCELONA

B

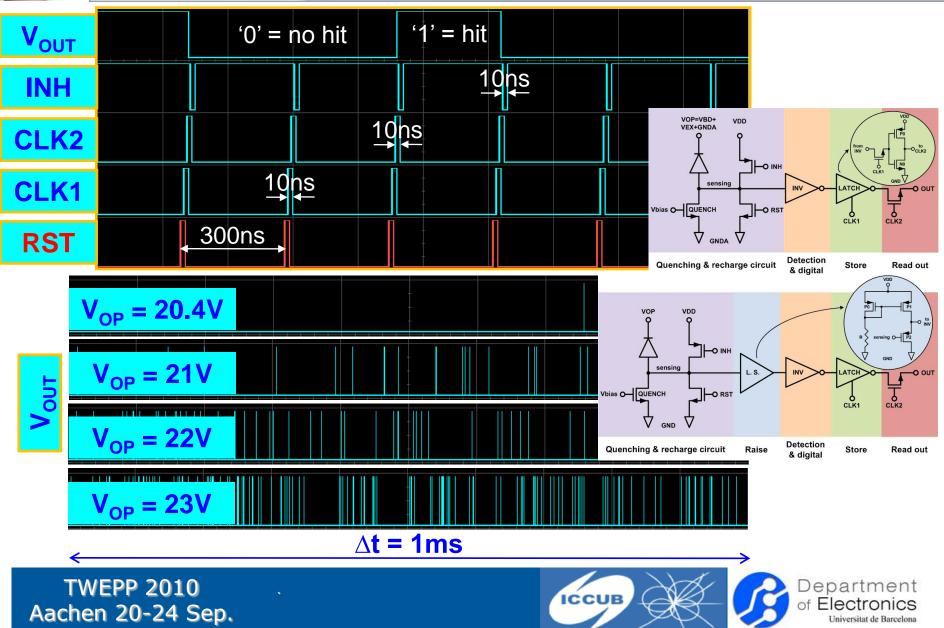

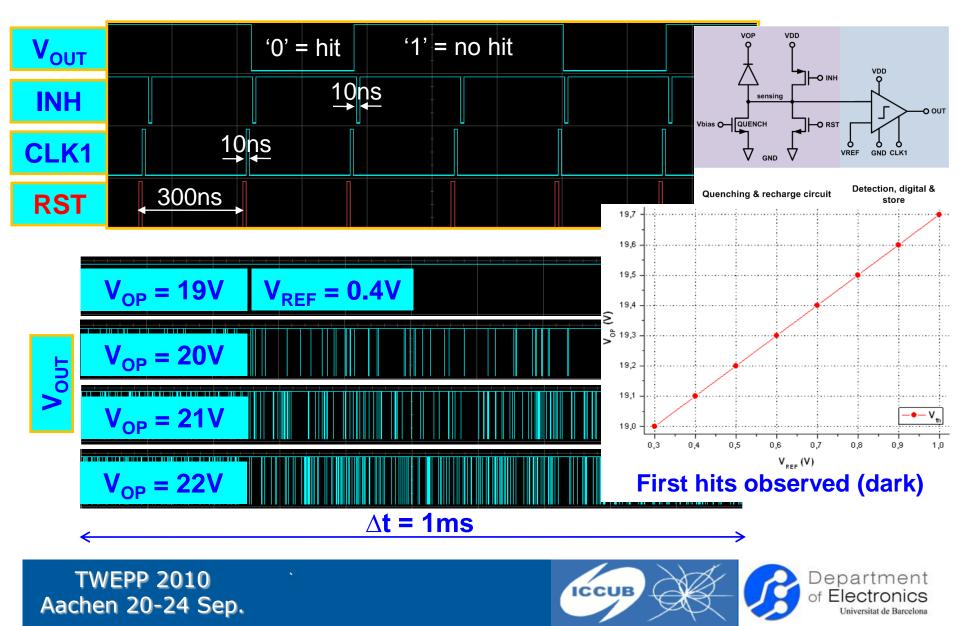

#### Test. Results.

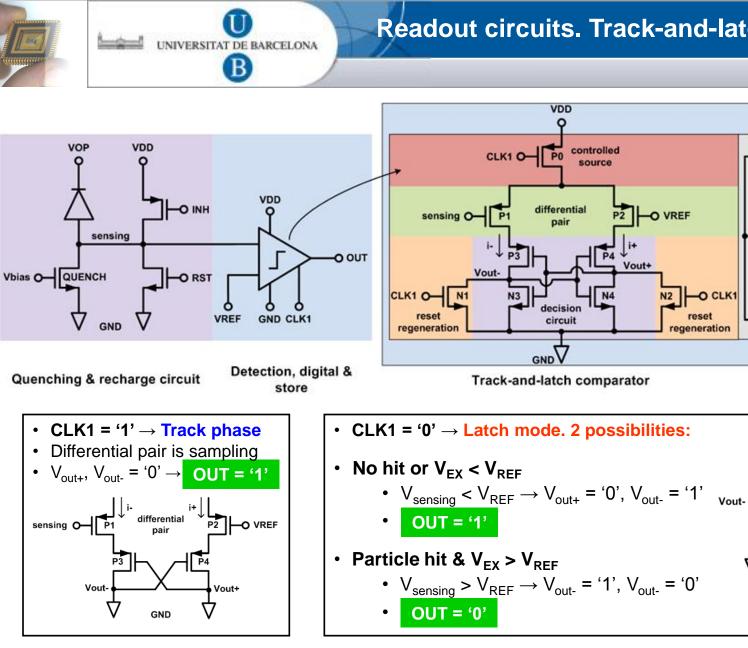

#### Readout circuits. Track-and-latch comparator.

ICCUB

VDD

P5

ont o

N5

**Output buffer**

i+ |

Department

Electronics

Universitat de Barcelona

Vout+

GND

GND

O OUT

#### Test. Results.

UNIVERSITAT DE BARCELONA

Detection.

B

#### Readout circuits. Comparison.

| Signal     | Value      |

|------------|------------|

| RST        | <b>'1'</b> |

| CLK1, CLK2 | '1'        |

| INH        | <b>'1'</b> |

| Propagation delay |             |

|-------------------|-------------|

| Readout circuit   | <b>'</b> 0' |

| 2 grounds scheme  | 1.8ns       |

| Level shifter     | 1.7ns       |

| Propagation delay |       |

|-------------------|-------|

| Readout circuit   | '1'   |

| 2 grounds scheme  | 0.5ns |

| Level shifter     | 1ns   |

Department

of

Electronics

Universitat de Barcelona

| Signal     | Value      |

|------------|------------|

| RST        | <b>'0'</b> |

| CLK1, CLK2 | '1'        |

| INH        | <b>'0'</b> |

ICCUB

#### Conclusions

#### • Conclusions

✓ GAPD-pixels are possible candidates for tracking systems in future linear colliders in order to have single BX resolution

#### $\checkmark\,$ We have designed GAPD-pixels with low dark count rate

- Standard 0.35µm HV-AMS CMOS technology

- Sensitive area of 20µm x 100µm

- Gated acquisition with an 'on' period of 10ns

- Readout electronics for low reverse bias overvoltage operation

- Quick response time and low power consumption

- ✓ We work to fit ILC requirements

- ? Coming soon...

- Fabricated chips have already been received

- Test is under development

- ? In the future...

- Study of different parameters of the sensor for the forward region tracker

- Arrays, 3D....

# Thank you very much for being such an attentive audience

Questions and comments are welcome

# **Back-up slides**

Universitat de Barcelona

|      | Technology                                                                                                              |                                                                                                                                  |  |

|------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

|      | HV-AMS 0.35 μm                                                                                                          | STM 0.13 μm                                                                                                                      |  |

| PROS | <ul> <li>✓ Low trap concentration</li> <li>✓ Reduced dark count</li> <li>✓ Lower storage data</li> </ul>                | <ul> <li>✓ High density of integration</li> <li>✓ High speed</li> <li>✓ No afterpulsing</li> <li>✓ Lower T dependance</li> </ul> |  |

| CONS | X Reduced speed $\rightarrow$ active recharge<br>X Afterpulsing $\rightarrow$ active quenching<br>X Higher T dependence | <ul> <li>X High dark count → gated mode</li> <li>X High storage data</li> </ul>                                                  |  |

|      |                                                                                                                         | HV-AMS<br>0.35µm                                                                                                                 |  |

|      | TWEPP 2010                                                                                                              | ICCUB Department<br>of Electronics                                                                                               |  |

Aachen 20-24 Sep.