## **3D-IC MPW runs for HEP**

### **Kholdoun TORKI**

Kholdoun.Torki@imag.fr

#### CMP

46, Avenue Félix Viallet,

38031 Grenoble, France

http://cmp.imag.fr

- Introduction

- Motivations for 3D-IC Integration

- CMC-CMP-MOSIS partnering on 3D-IC

- Process Overview

- MPW runs

- Design Platform features for 3D-IC

- 3D-IC automatic Place & Route

- Conclusion

### **CMP created in 1981**

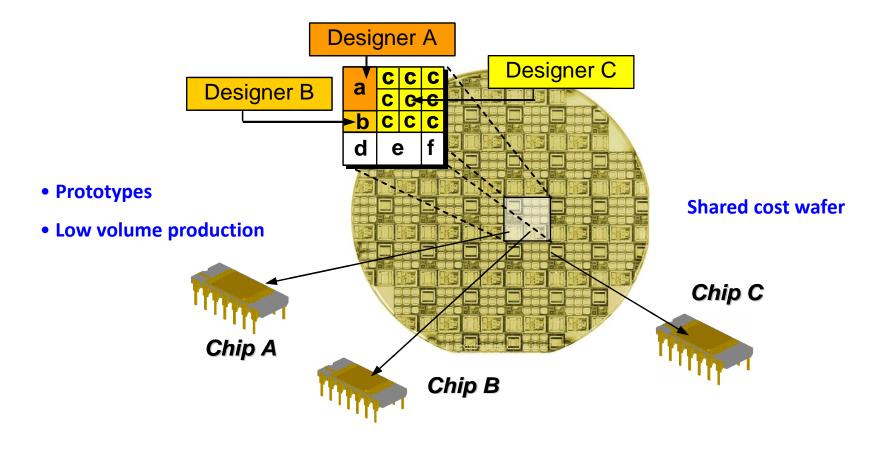

- Offering industrial quality process lines

(University process lines cannot offer a stable yield)

- Design-kits to link CAD and MPW, to facilitate the design.

- Customer base development

- + Universities / Research Labs

- + Industry

- + 1000 Institutions in 70 countries

- Non-profit, Non-sponsored

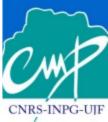

Multi-Project Wafer runs allow to share the price by sharing the reticle area.

- □ Prototype fabrication.

- **D** Low volume productions (some hundreds to hundred thousands parts)

### Introduction

- Motivations for 3D-IC Integration

- CMC-CMP-MOSIS partnering on 3D-IC

- Process Overview

- MPW runs

- Design Platform features for 3D-IC

- 3D-IC automatic Place & Route

- Conclusion

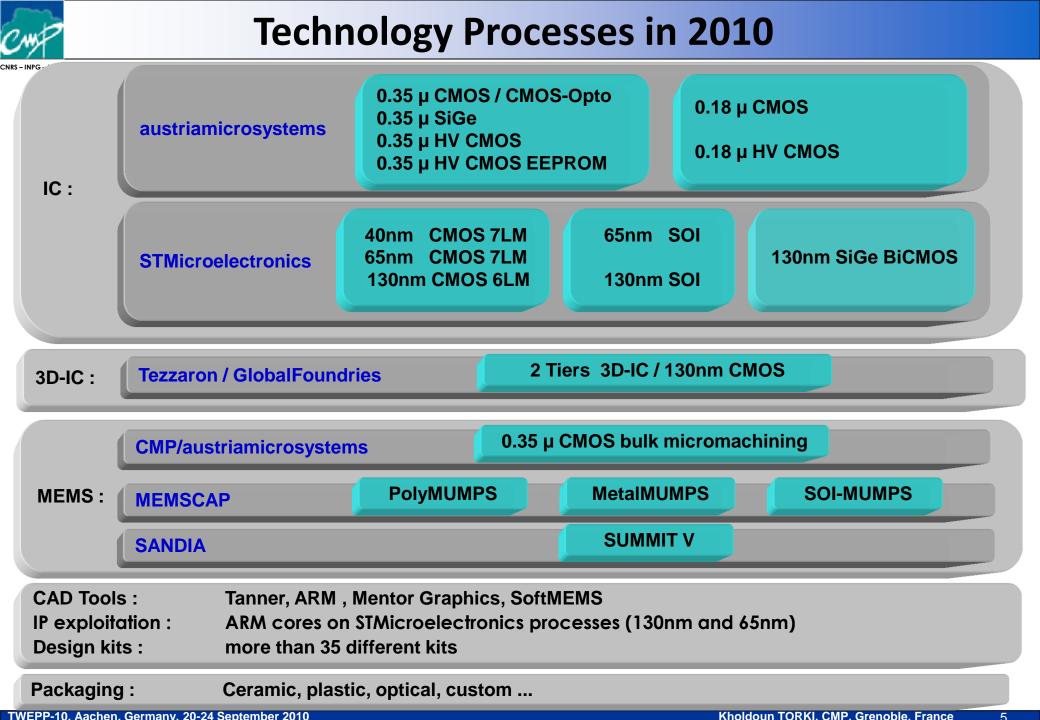

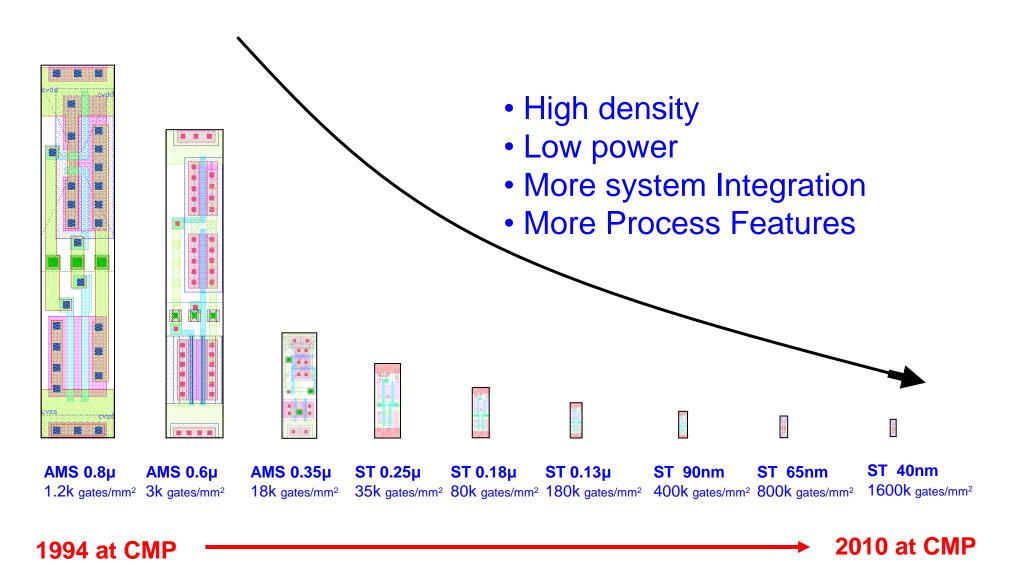

## **CMOS Process Roadmap**

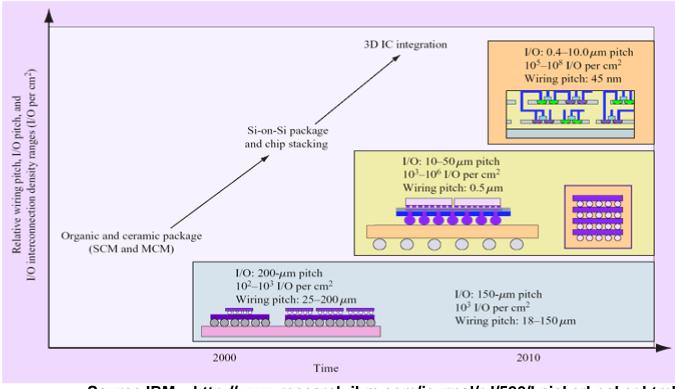

### **3D-IC Integration : The Other Path for Scaling**

Source IBM http://www.research.ibm.com/journal/rd/526/knickerbocker.html

- Moore's law by scaling conventional CMOS involves huge investments.

- 3D IC processes : An opportunity for another path towards continuing the scaling, involving less investments.

- Like for conventional CMOS, infrastructures are needed to promote 3D-IC integration, making it available for prototyping at "reasonable" costs.

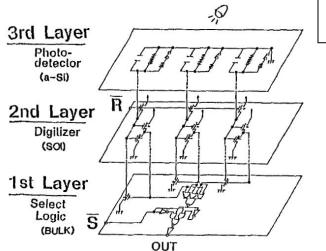

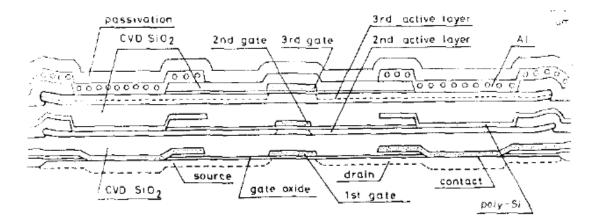

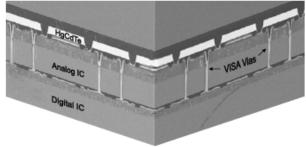

Fig.8 a-Si photo sensor and processing circuits in 3-staked layers (after Mihashi)

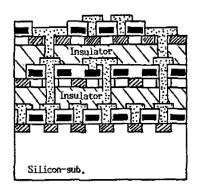

Fig.l Schematic drawing of 3-D IC consisting of monolithic multi-layer structure.

Akasaka, Y., and Nishimura, T., "Concept and Basic Technologies for 3-D IC Structure" IEEE Proceedings of International Electron Devices Meetings, Vo. 32, **1986**, pp. 488-491.

Fig.4 SEM cross sectional photograph and schematic drawing of planarized tripply-stacked IC structure.

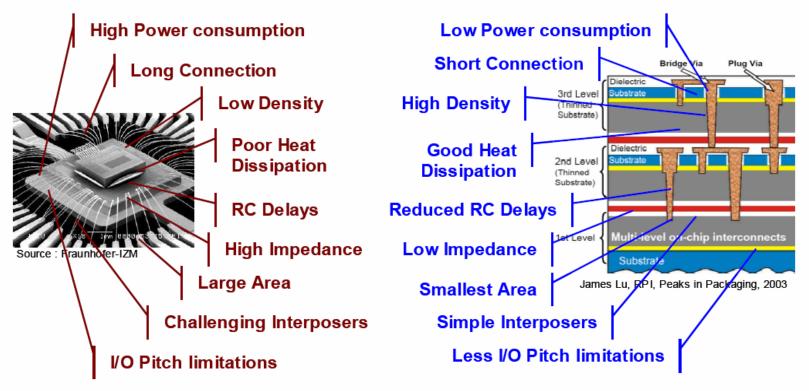

TSV (Through-Silicon-Via) electrodes can provide vertical connections that are both the shortest and the most plentiful.

TSV interconnects provide solutions to many limitations of current SiP and Chip Stacking methods.

Ecole Polytechnique Paris - 3D Technical Symposium; November 2007

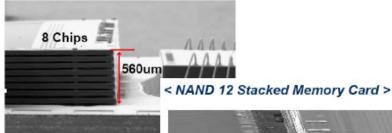

# Industrial Applications

- There are two 3D areas that are receiving a lot of attention.

- Stacked memory chips and memory on CPU

- IBM expected to provide samples later this year

- Both IBM and Samsung could be in production next year (2008)

- Imaging arrays (pixelated devices)

- Working devices have been demonstrated by MITLL, RTI, and Ziptronix

- Much work is supported by DARPA

- Pixel arrays offer the most promise for HEP projects.

#### < NAND 8 Stacked Memory Card >

Samsung - 30 um laser drilled vias in 70um chips

LHC-ILC Workshop on 3D Integration Techniques

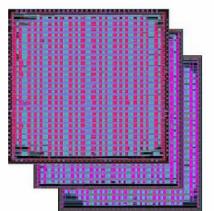

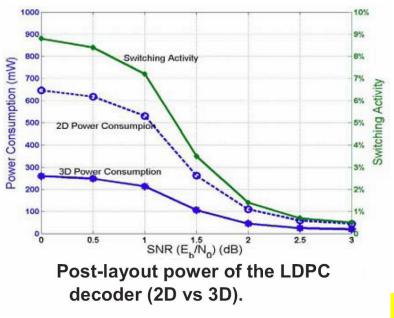

Final layout view of 3D LDPC structure.

#### "Implementing a 2-Gbs 1024-bit ½-rate Low-Density Parity-Check Code Decoder in Three-Dimensional Integrated Circuits"

Lili Zhou, Cherry Wakayama, Robin Panda, Nuttorn Jangkrajarng, Bo Hu, and C.-J. Richard Shi University of Washington

International Conference on Computer Design, ICCD, Oct. 2007

|                   | <u> </u>     |                   |  |  |  |

|-------------------|--------------|-------------------|--|--|--|

|                   | 2D design    | 3D design         |  |  |  |

| Area (mm*mm)      | 18.238*15.92 | (6.4*6.227)*3     |  |  |  |

|                   | =290.35      | = 119.56          |  |  |  |

| Total wire length | 182.42       | 22.39+22.57+22.46 |  |  |  |

| (m)               | 182.42       | =67.42            |  |  |  |

| Max WL before     |              |                   |  |  |  |

| buffer insertion  | 13.82        | 8.68              |  |  |  |

| (mm)              |              |                   |  |  |  |

| Max WL after      |              |                   |  |  |  |

| buffer insertion  | 4            | 4                 |  |  |  |

| (mm)              |              |                   |  |  |  |

| Buffer used       | 32900        | 24636             |  |  |  |

| Clock skew (ns)   | 2.33         | 1                 |  |  |  |

| Power dissipation | 646.2        | 260.2             |  |  |  |

| (mw)              | 040.2        |                   |  |  |  |

#### **Comparison between 3D and 2D designs**

**Performance Factor (Area \* Timing \* Power) = 14**

- Introduction

- Motivations for 3D-IC Integration

- CMC-CMP-MOSIS partnering on 3D-IC

- Process Overview

- MPW runs

- Design Platform features for 3D-IC

- 3D-IC automatic Place & Route

- Conclusion

## **CMC-CMP-MOSIS partnering on 3D-IC**

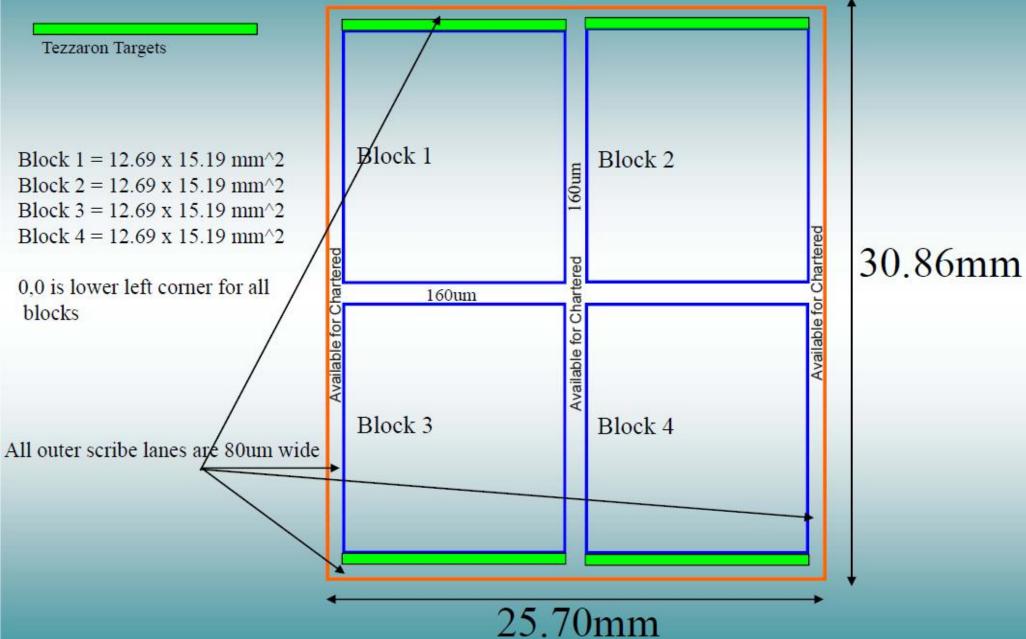

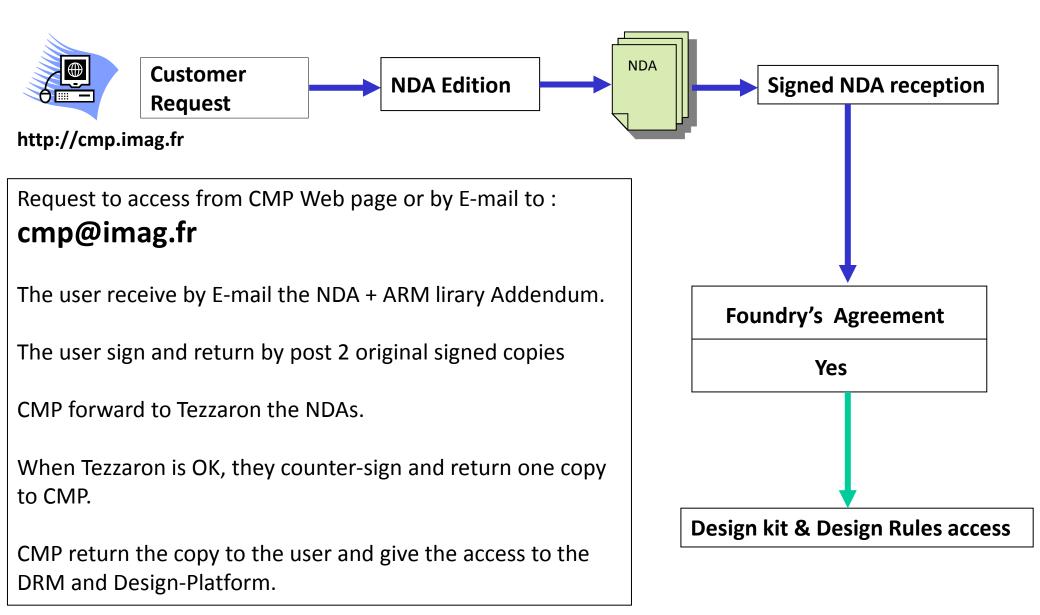

**CMP/CMC/MOSIS** partner to introduce a 3D-IC process

Grenoble, France, 22 June 2010, CMP/CMC/MOSIS are partnering to offer a 3D-IC

MPW service based on Tezzaron's SuperContact technology and GLOBALFOUNDRIES 130nm CMOS.

The first MPW run is targeting January 2011:

- 2-tier face-to-face bonded wafers

- 130nm CMOS process for both tiers

- Top tier exposing TSV and backside metal pads for wire bonding.

A design-kit supporting 3D-IC design with standard-cells and IO libraries is available.

Further MPW runs will be scheduled supporting process flavors (multiple tiers beyond

2, different CMOS flavors for different tiers, ...) driven by user requirements.

Potential users are encouraged to contact **CMP** for details : **cmp@imag.fr**

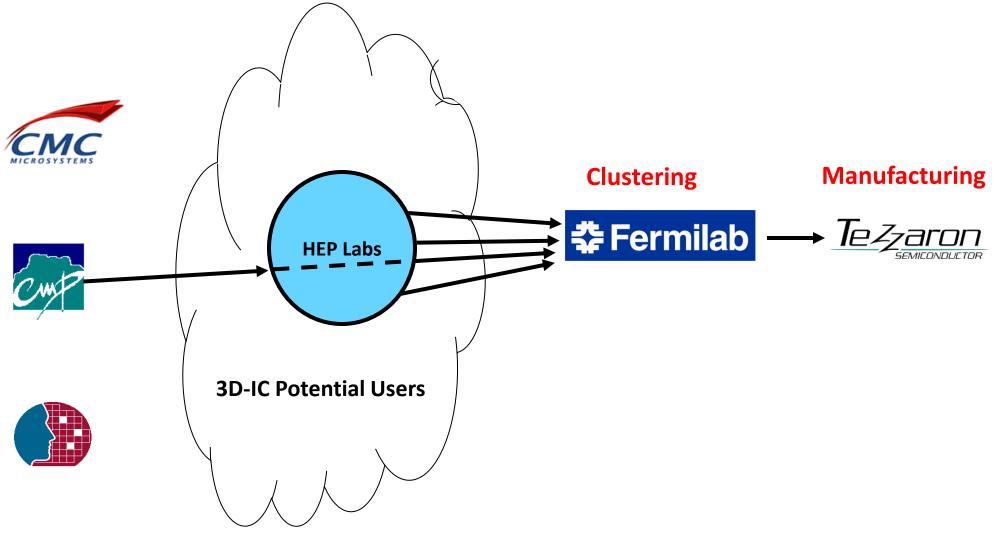

### CMC / CMP / MOSIS partnering for 3D-IC process access

• Stimulate the activity by sharing the expenses for manufacturing.

• Join forces for the technical support, and dedicate the roles for each partner.

• Make easier the tech support for local users respectively by each local center.

• Because there is no standard for the 3D-IC integration, it is urgent to setup an infrastructure making possible a broad adoption of 3D-ICs. That will have a beneficial effect on prices, more frequent MPW runs, and more skilled engineers.

## **CMC - CMP - MOSIS Cooperation**

- All 3 in contact with TEZZARON to offer MPW runs service

- New users are presently accessing to the process.

- Roles of each partner :

- MOSIS is the main contractor with Tezzaron.

- MOSIS will cluster reticles.

- CMP is the technical support center.

- All three address their respective regions for the access to the process and the local technical support.

- Target a First MPW run in March 2011.

## **CMC - CMP - MOSIS Cooperation**

- CMC supporting Canadian Customers

- CMP supporting European Customers

- MOSIS supporting US Customers

- Each may support other locations

- Introduction

- Motivations for 3D-IC Integration

- CMC-CMP-MOSIS partnering on 3D-IC

- Process Overview

- MPW runs

- Design Platform features for 3D-IC

- 3D-IC automatic Place & Route

- Conclusion

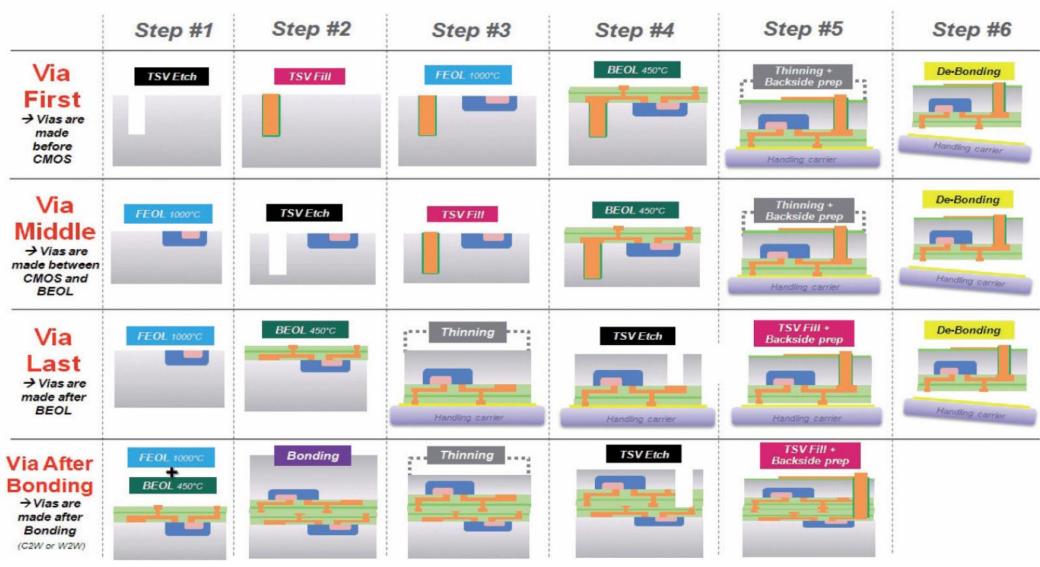

## **3D TSV via integration MAIN scenarios**

#### **Source Yole Development**

| Interconnection Type           | Line Width<br>(µm) | Line Thickness<br>(µm) | Line Resistance<br>(Ohm/cm) | Max Length<br>(cm) |

|--------------------------------|--------------------|------------------------|-----------------------------|--------------------|

| Direct Bond Interface<br>(DBI) | 2-100              | 2-100                  | 0                           | 0                  |

| Through Si Via<br>(TSV)        | 1.2-100            | 1.2-100                | 500-1000                    | 5-100              |

| On-Chip                        | 0.1-2              | 0.1-2                  | 100-1000                    | 0.1-1.5            |

| Thin-film                      | 10-25              | 5-8                    | 1.25-4                      | 20-45              |

| Ceramic                        | 75-100             | 16-25                  | 0.4-0.7                     | 20-50              |

| Printed Circuit Board          | 60-100             | 30-50                  | 0.06-0.08                   | 40-70              |

| Shielded Cables                | 100-450            | 35-450                 | 0.0013-0.033                | 150-500            |

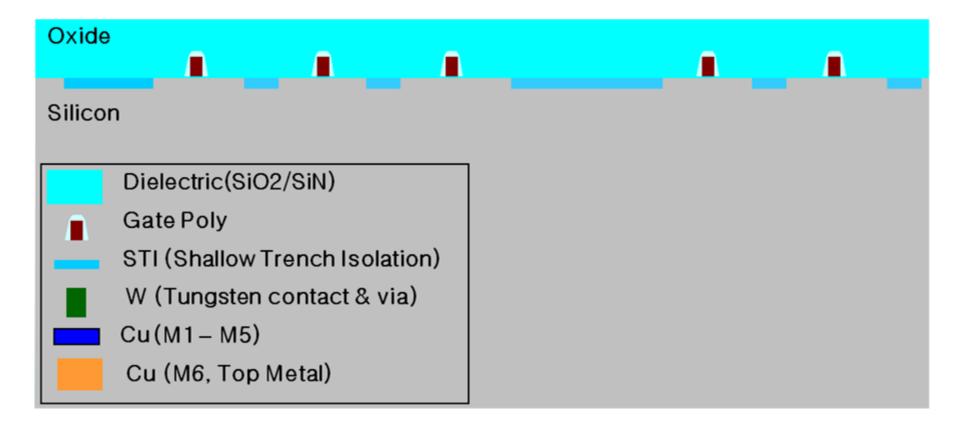

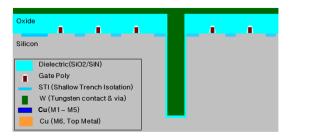

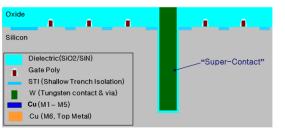

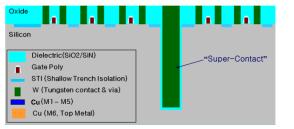

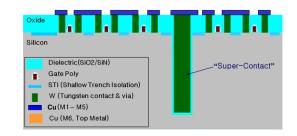

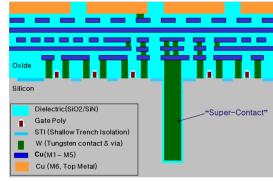

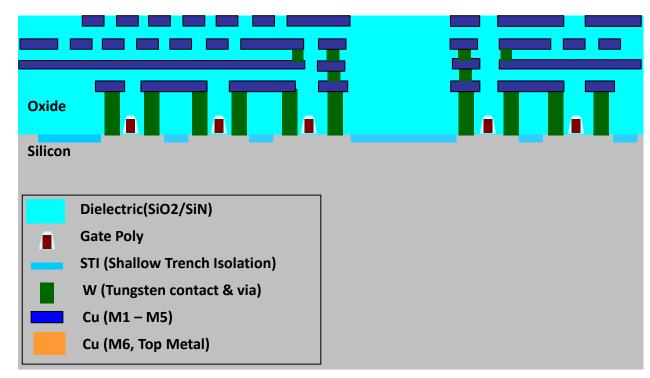

### Starting wafer in 130nm (5 Cu metal layers + 6<sup>th</sup> Cu metal as BDI)

### **Tezzaron Process Flow for TSV and DBI (using Via Middle process)**

CNRS – INPG – UJF

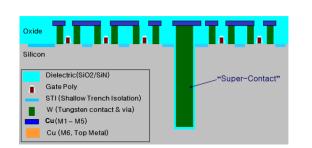

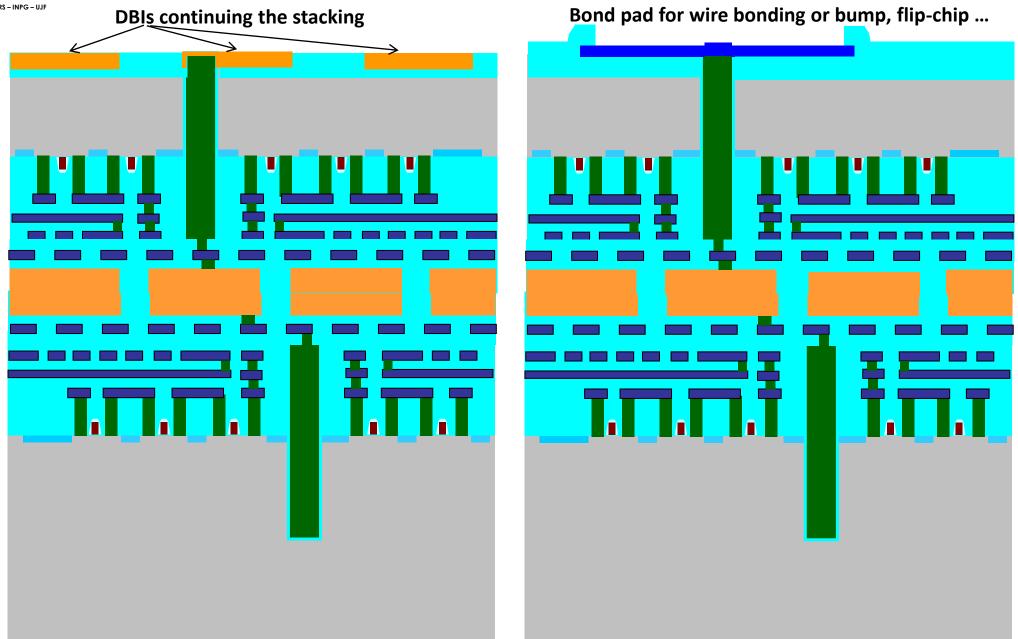

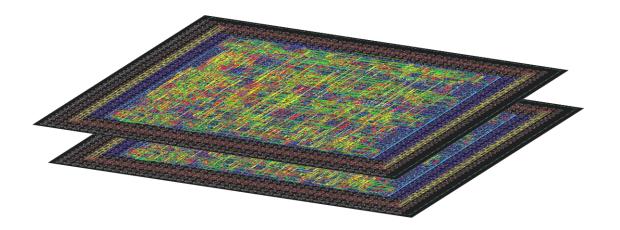

### Resulting 2-tier 3D-IC integration TSV and DBI (Via Middle Process)

**Top Tier** (10um thickness) **Bottom Tier** (Handle wafer)

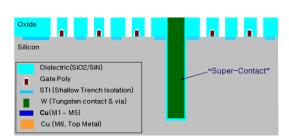

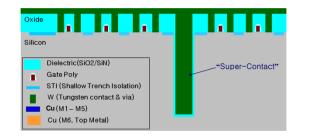

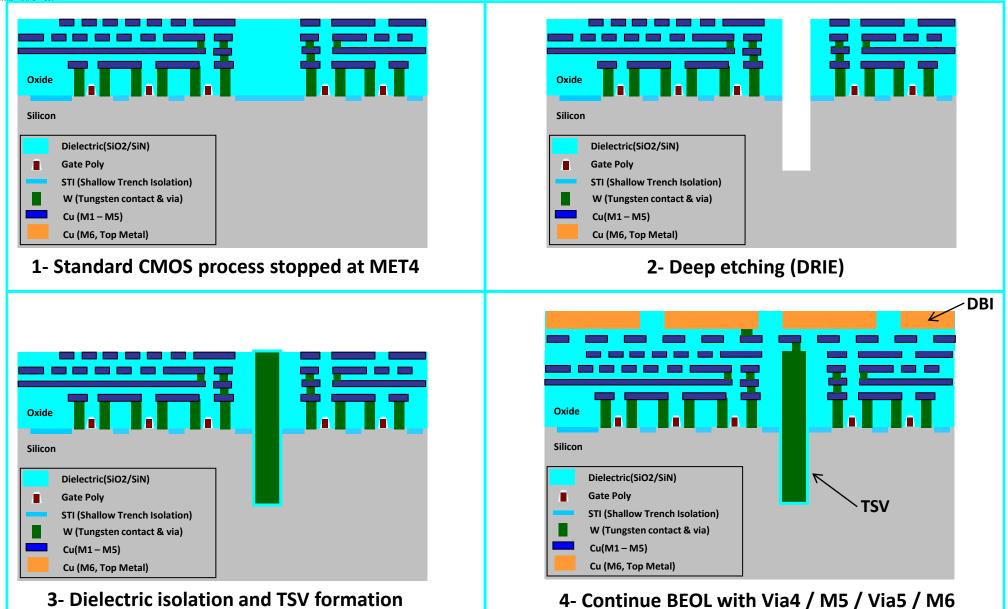

### New Tezzaron Process Flow using "Near End of Line" TSV

#### Starting wafer in 130nm stopped at Metal 4

130nm Chartered Low Power

Options: Dual gate 2.5, 1.5V

TSV enabled

Deep Nwell

Lvt implant

6 Cu Metal Layers : 5 usable plus a 6th as BDI

No MIM, No High resist poly

### New Tezzaron Process Flow using "Near End of Line" TSV

### New Tezzaron Process Flow using "Near End of Line" TSV

Advantages of "Near End of Line" :

- The process can be done on any wafer from any foundry, provided that BEOL is stopped at Metal 4. The post-process for TSV and DBI is independent from the foundry.

- As a consequence, it allows mixing different process nodes 130nm / 65nm from different foundries, or any combination like assembling SiGe BiCMOS and CMOS.

**Disadvantage of "Near End of Line" :**

• The access to the TSV is only possible with a Via from Metal5. That makes long paths and serial resistances through the 5 Vias from the MOS to the TSV.

- Introduction

- Motivations for 3D-IC Integration

- CMC-CMP-MOSIS partnering on 3D-IC

- Process Overview

- MPW runs

- Design Platform features for 3D-IC

- 3D-IC automatic Place & Route

- Conclusion

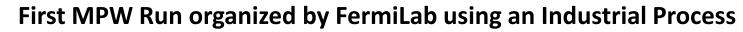

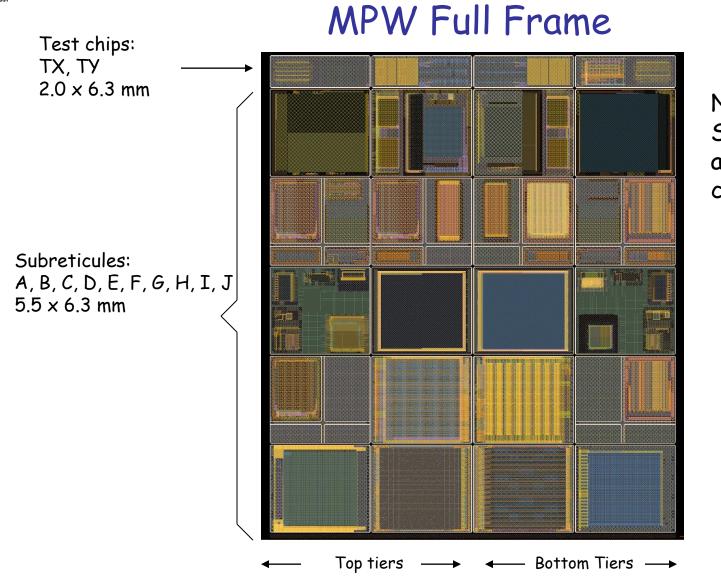

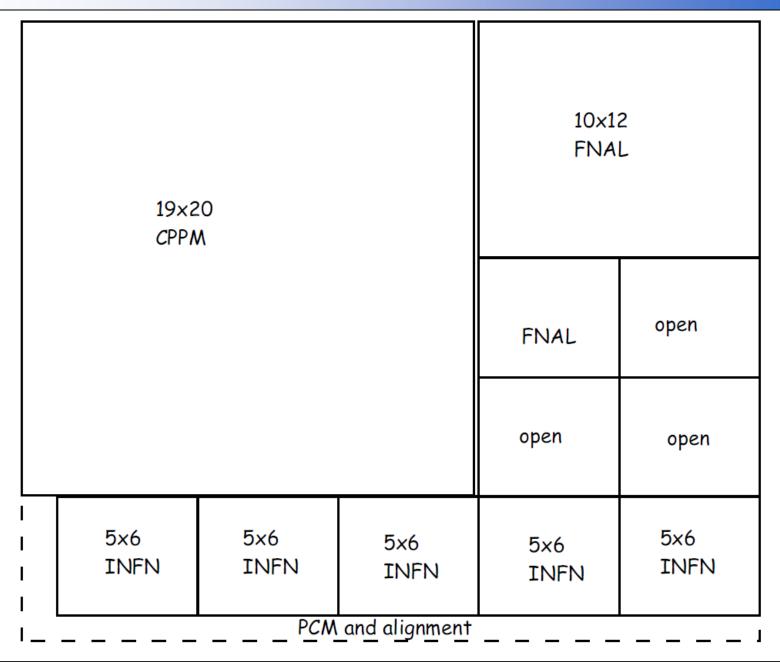

### **3D Consortium : 1st MPW run**

Notice Symmetry about vertical center line

Source FermiLab (3D Consortium Meeting)

#### CMC-CMP-MOSIS partnering to offer 3D-IC MPW runs

### **Critical mass will allow frequent MPW runs and low pricing**

### CMC-CMP-MOSIS : 1<sup>st</sup> MPW run Planned March 2011

- Introduction

- Motivations for 3D-IC Integration

- CMC-CMP-MOSIS partnering on 3D-IC

- Process Overview

- MPW runs

- Design Platform features for 3D-IC

- 3D-IC automatic Place & Route

- Conclusion

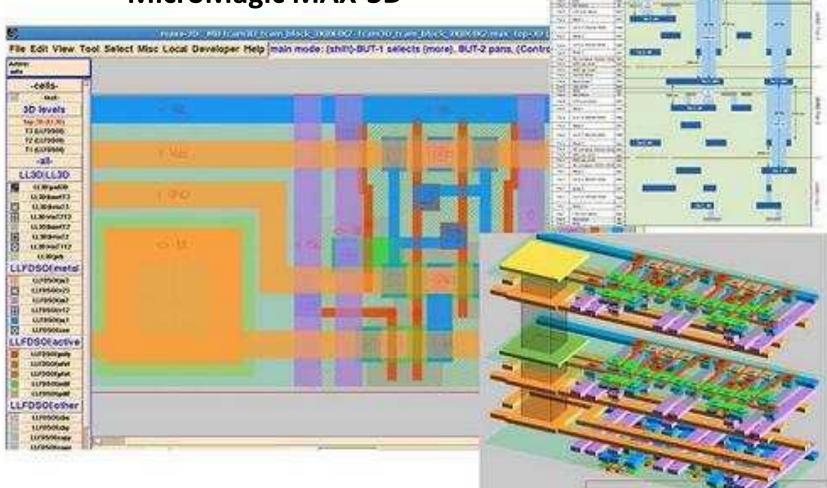

- Making a common root installation for the different parts of the Design Platform

- PDK

- Libraries

- Memory compilers

- Utilities

- Tutorials

- Defining a unique variable for the root installation. All the modules inside refer to this unique variable.

Making the Design Platform portable to any site without configuration scripting. The user need just to define the path to this variable.

- The PDK has been revisited organizing its content.

- Organize the different modules by tools

- Redefine the Cadence IC configuration files to include missing features

- Correcting some definitions (libInit.il)

- Reorganize the utilities

- Choice between different layers palettes.

- Unify the cellviews inside a single database (CDB format)

(can be done the same way when the OpenAcess data format will be available)

- Define setup files pointing to the libraries :

- For Cadence DFII + Mentor/Calibre

- For Synopsys Design Compiler

- For Encounter Place & Route tools.

TDP\_2010q2v1 : Tezzaron Design Platform

CSM013LP LVT SC 2007q2v1 : Chartered LP LVT Core cells CSM013LP SC 2005q1v1 : Chartered LP standard VT Core cells CSM013 IO GP IL 2005q3v2 : Chartered In Line IO cells CSM013 IO GP ST 2005q2v1 : Chartered In Line IO cells CSM013 MEM COMPILERS : Chartered Memory compilers MMI PDK I: MicroMagic PDK part I MMI PDK II : MicroMagic PDK part II **README NCSU** UTILITIES 2010q2v1 : Utilities provided by the community chrt13lprf DK009 Rev 1C TSC 1C : Chartered/Tezzaron PDK **Doc**: Documentation Install : Installation utilities and setup environments tutorials : Here comes the different design-flows tutorials

#### chrt13lprf\_DK009\_Rev\_1C\_TSC\_1C : Chartered PDK including Tezarron layers

Chartered.013lp.ReleaseNotes Chartered.013rf.ReleaseNotes MapTables : layers map tables : Encounter / ARM libs assura : QRC extraction / Dummies filling program Calibre : 3DDRC / 3DLVS / Dummies filling chrt013lp : Technology library + devices (active & passive) chrt013rf : Complementary library with RF devices doc : Documentations : Design-rules / design guides (Chrtrd + Tezzaron) eldo: Model files for Eldo hspice : Model files for Hspice skill : Skill routines for 3D LVS spectre : Model file for Spectre src : C program fro NCSU preprocessing for 3D LVS.

Each Library of standard-cells or IO pads is organized as follows :

**README.copyright** README.csm013lp-lvt\_sc-x2\_2007q2v1 **README.fe** license apollo : Synopsys backend views for P&R cds cdb : Cadence database with all cellviews cds oa : Cadence OpenAcess format with all cellviews cell list doc : Documentation edif : Edif format for symbols gds2 : Physical layouts in GDSII format lef : LEF format for P&R lvs netlist : CDL netlists for LVS primetime : Perl script backannotation for Primetime synopsys : Frontend and Backend libraries for Synopsys Digital Flow verilog : Verilog libraries vhdl: VHDL libraries

#### HEP contributing Programs, Libraries, and Utilities have been included in the Design Platform

DBI (direct bonding interface) cells library. (provided by FermiLab)

3DPad template compatible with the ARM IO lib. (provided by IPHC)

Preprocessor for 3D LVS / Calibre (provided by NCSU)

Skill program to generate an array of labels (provided by IPHC)

Calibre 3D DRC (provided by Univ. of Bonn)

Dummies filling generator under Assura (provided by CMP)

Basic logic cells and IO pads (provided by FermiLab)

Floor-planning / automatic Place & Route using DBIs, and TSVs (provided by CMP)

Skill program generating automatically sealrings and scribes (provided by FermiLab)

MicroMagic PDK (provided by Tezzaron/NCSU)

NO FILL X: 12.500 drw. Y: -4.115 (F) Select: 0 DRD: OFF Dist: Cmd: dX: dY: 2 TSV. TSCSuperCnt drw Tools Design Window Create Edit Verify Connectivity Options Routing Assura Calibre Help TSCBackMet0 drw Q **Back Metal** ISCBackMet0 [1b1] Calibre Integration 💋 TSCBackMet1 drw Ę TSCBackMet1 lbl Back Pad-TSCBPad drw Q drw SRAM TSC Assura drw PR BNDRY drw NWELL DNWELL drw LDMOS XTOR mar drw COMP POLY2 drw POLY2 1b1 PPLUS drw NPLUS drw CNT drw MET1 drw MET1 1b1 VIA1 drw MET2 drw MET2 1b1 VIA2 drw MET3 drw MET3 1b1 VIA3 drw / MET4 drw / MET4 1b1 VIA4 drw MET5 drw MET5 1b1 mouse L: mouseSingleSelectPt M: leHiMousePopUp() R:hiZoomAbsoluteScale(hiGetCurrentWi VIATOP drw > DBI METITOP drw

TWEPP-10, Aachen, Germany, 20-24 September 2010

# **Technology Files fully supported by Tezzaron**

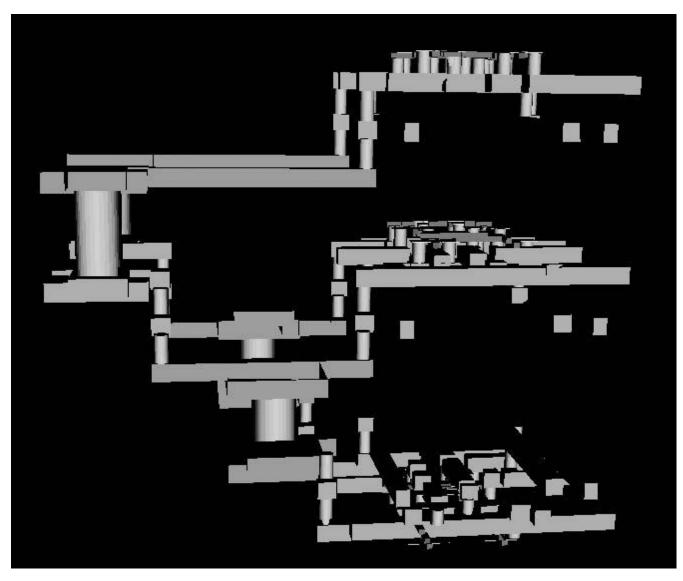

## MicroMagic MAX-3D

### Should we develop an interface to generate VRML descriptions from Virtuoso Layout ?

# Users having access to the Design Platform

CPPM, Marseille Tezzaron Semiconductor, USA **IPHC**, Strasbourg LAL, Orsay FermiLab, USA LPNHE, Paris France **IRFU, CEA Saclay** North Carolina State University, USA LAPP, Annecy-Le-Vieux \* ENSTA PARISTECH, Paris \* MOSIS, USA CMC Microsystems, Canada INFN, Roma **INFN**, Pavia University of Sherbrooke, Canada INFN, Pisa Italy University of Bologna \* + Other centers supported by MOSIS and CMC University of Perugia Not listed here. University of Bonn, Germany University of Barcelona, Spain IMSE-CNM-CSIC, Sevilla, Spain University of Turku, Finland **New Users** Acreo AB, Norrköping, Sweden Norwegian University, Trondheim, Norway Monash University, Clayton, Australia

**19 Users in Europe**

- Introduction

- Motivations for 3D-IC Integration

- CMC-CMP-MOSIS partnering on 3D-IC

- Process Overview

- MPW runs

- Design Platform features for 3D-IC

- 3D-IC automatic Place & Route

- Conclusion

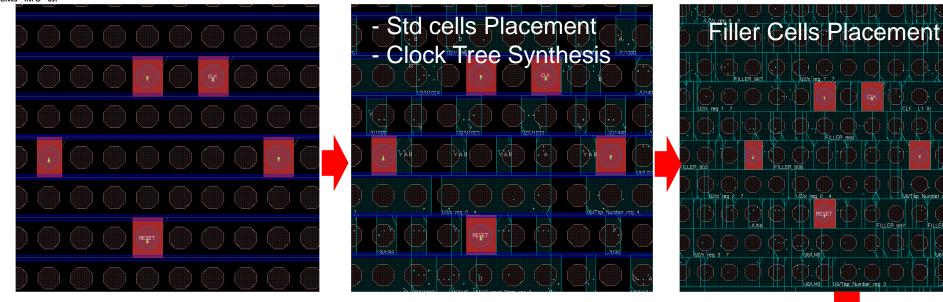

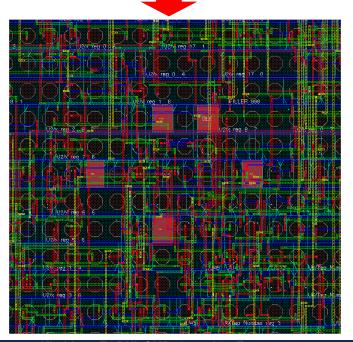

### System Level Partitioning

3D Floor-Planning DBI, TSV, IO placement

Automatic Place & Route

Extraction, Timing Analysis

Design exploration at system level

Design exploration at the physical level DBI, TSV, and IO placement & optimization

Cells and blocks place & route can be done tier by tier

To be done for each tier, then combined for backannotation to the 3D top level system

Physical verification 3D DRC, 3D LVS

Dummies Filling

#### Final 3D DRC

Similar to the full-custom design flow

- Encounter natively refuses to make the routing for pins on DBIs.

- A custom script solved the problem. It's a workaround.

- The resulting layout is compliant to the Tezzaron DRC, LVS etc ...

DBI array generation + P&R

DBI completely routed through the lower metal layers

Saving the floor plan for the bottom tier, and apply it for top tier so the automatic Place & Route run the placement and routing taking into account the DBI locations.

The place & route for both tiers is optimal for timing, buffer sizing and power performance.

# This should result in a "correct by construction" design.

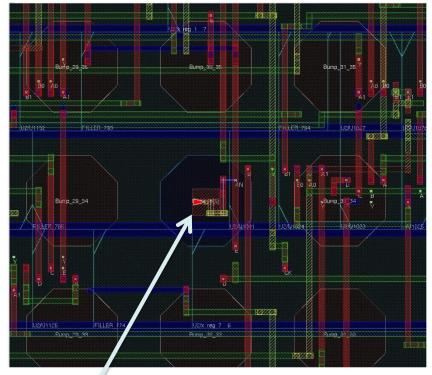

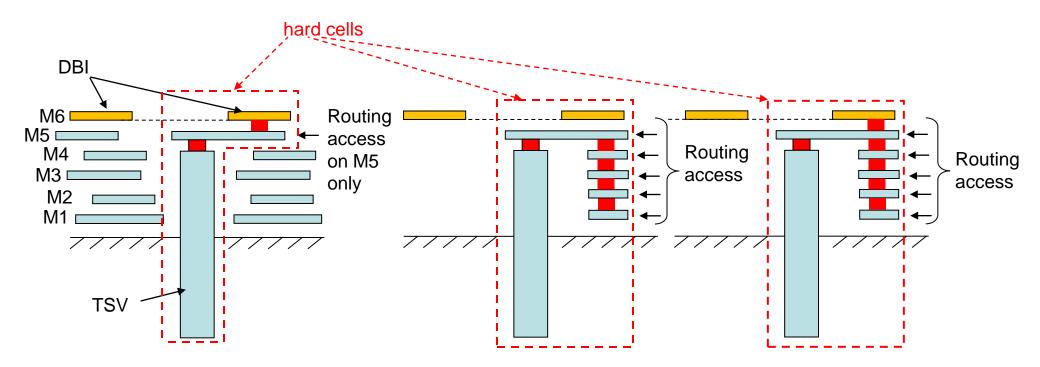

### 3 ways investigated and solved for P&R using TSV :

1) Using a combined TSV / DBI cell allowing a straight vertical routing across the tiers. Scripting allowing the automatic placement, then P&R is done automatically. Access is available on M5. The router decides how to make the wiring to the pin. (RDL routing)

2) Using a separated TSV, allowing the router to connect to any of the metal layers (except M6).

3) Using a combined TSV / DBI cell with pins for routing on all metal layers (except M6)

### Create Bump Array

### Floorplan > Flip Chip > Create bump Array...

Specify the array Name, number of bumps, pitch, ... Then click OK.

To save an IO file with this bump array choose the following menu: Design > Save > I/O File...

| Create Bump Array                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| Bump Array<br>Name: array_2                                                                                                                  |

| Bump Cell BDI                                                                                                                                |

| Bump Matrix                                                                                                                                  |

| ◆ Full Matrix                                                                                                                                |

| Rows: 53<br>Columrs: 53<br>Staggor Full<br>Permeter Matrix<br>Outer Ring 1<br>Stagger Outer<br>Center Columns<br>Center Rows<br>Stagger Core |

| Create in Area           X1:         0.0         X2:         682.0           V1:         0.0         V2:         682.0                       |

| Bump Spacing<br>Bump Pitch<br>Horizontal: 5<br>Vertical: 5<br>Edge Spacing<br>DX: 210<br>DY: 210                                             |

| Ok Apply <u>Cancel II</u> elp                                                                                                                |

#### Floorplan > Flip Chip > Assign Signal...

- 1. Select the IO signal in the list

- 2. Select the bump to be assigned

- 3. Click "Assign". The selected bump become blue.

|                                |                    | Ass           | ign/   | Unassign Signa | als         |          |                                                  | Encounter ® Digital Implementation System RTL-to-GDSII 8.1 - /cmp/ho                                                                                       |

|--------------------------------|--------------------|---------------|--------|----------------|-------------|----------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal List —                  |                    |               |        |                |             |          |                                                  | <u>D</u> esign <u>E</u> dit Syrthesis Partitic <u>n E</u> loorplan Po <u>w</u> er <u>P</u> lace <u>C</u> lock <u>Boute</u> <u>Timing</u> <u>SI V</u> erify |

| IO Signa                       | Criver             | Cell          | Pin    | Location       | Tile/Bump   | Tile Pin | Loc                                              |                                                                                                                                                            |

| Filter_In[2]                   | io_In2             | PIC P         |        | x=00 y=411.0   |             |          |                                                  |                                                                                                                                                            |

| Filter_In[1]                   | io_In <sup>-</sup> | PIC P         |        | x=00 y=341.0   |             |          |                                                  |                                                                                                                                                            |

| "liter_in[0]                   |                    | PIC P         |        | x=00 y=271.0   |             |          |                                                  |                                                                                                                                                            |

| <br>С_К                        | io_In_CLK          | PIC P         |        | x=218.5 y=0.0  |             |          |                                                  |                                                                                                                                                            |

| ESET                           | io_In_RESET        | PIC P         |        | x=306.0 y=0.0  |             |          |                                                  |                                                                                                                                                            |

| DC_Busy                        | io_In_ADC_busy     | PIC P         |        | x=333.5 y=0.0  |             |          |                                                  |                                                                                                                                                            |

| DC_Convetb                     | (nul)              |               | nu I)  |                |             |          |                                                  |                                                                                                                                                            |

| _<br>DC_Rd_csb                 | (nul)              |               | nul)   |                | Bimp_22_26  |          | x=318.3                                          |                                                                                                                                                            |

| ilter_Out'7]                   | (nul)              |               | nul)   |                | Bump_35_33  |          | x=383.3                                          | Area Density                                                                                                                                               |

| liter_Out 6                    | (nul)              |               | nul)   |                | Bumb_29_33  |          | X=353.3                                          |                                                                                                                                                            |

| ilter_Out'5]                   | (nul)              |               | nul)   |                | Bump_23_33  |          | ×=323.3                                          |                                                                                                                                                            |

| Iter_Out[4]                    | (nu l)             | `             | nu I)  |                | Bump_17_33  |          | x=293.3                                          |                                                                                                                                                            |

| Iter_Out'3]                    | (nul)              |               | nul)   |                | Bump_35_19  |          | x=383.3                                          |                                                                                                                                                            |

| ilter_Out[2]                   | (nul)              |               | nul)   |                | Dumo_20_10  |          | ×-353.3                                          | & \Box \Box \Box \Box \Box \Box \Box \Box                                                                                                                  |

| ilter_Out'1]                   | (nu l)             |               | nul)   |                | Bump_23_19  |          | x=323.3                                          |                                                                                                                                                            |

| ilter_Out[0]                   | (nul)              | `             | nul)   |                | Bump_17_19  |          | x=293.3                                          | ₩ ₩ ₩ ₩ ₩ ₩ ₩ ₩ ₩ ₩ ₩ ₩ ₩ ₩ ₩ ₩                                                                                                                            |

| mor_oariol                     | (                  |               |        |                | 50110_11_10 |          |                                                  |                                                                                                                                                            |

|                                |                    | Num           | her of | flo Signals 21 |             |          |                                                  |                                                                                                                                                            |

|                                |                    |               |        |                |             |          |                                                  | <b>E O O O O O O O O O O O O O O O O O O O</b>                                                                                                             |

| ssign to Tiles                 | /Bumps             |               |        |                |             |          |                                                  |                                                                                                                                                            |

| <ul> <li>n Select :</li> </ul> | Set .              |               |        |                |             |          |                                                  |                                                                                                                                                            |

| 🔶 in Created                   | lOrder             | Set Orde      | er: /  | ≏s Is          | -           |          |                                                  |                                                                                                                                                            |

| ↓ Closest                      |                    |               |        |                |             |          | Densty Maa                                       |                                                                                                                                                            |

| V                              |                    |               |        |                |             |          |                                                  |                                                                                                                                                            |

| let Net Wire W                 | /idth              |               |        |                |             |          |                                                  | <u> </u>                                                                                                                                                   |

| Wire Width: Set                |                    |               |        |                |             |          | <u>ାରି ଓ ଓ ଓ ଓ ଓ ଓ ଓ ଓ ଓ ଓ ଓ ଓ ଓ ଓ ଓ ଓ ଓ ଓ ଓ</u> |                                                                                                                                                            |

| 1                              |                    |               |        |                |             |          |                                                  | <u> </u>                                                                                                                                                   |

| <u>A</u> ssig                  | r                  | <u>U</u> nas: | elen [ |                | Done        |          | ц.                                               |                                                                                                                                                            |

| <u></u>                        |                    | Unas          | งยุก   |                |             |          | <u><u>H</u></u>                                  | Q 1(332.952, 273.339)                                                                                                                                      |

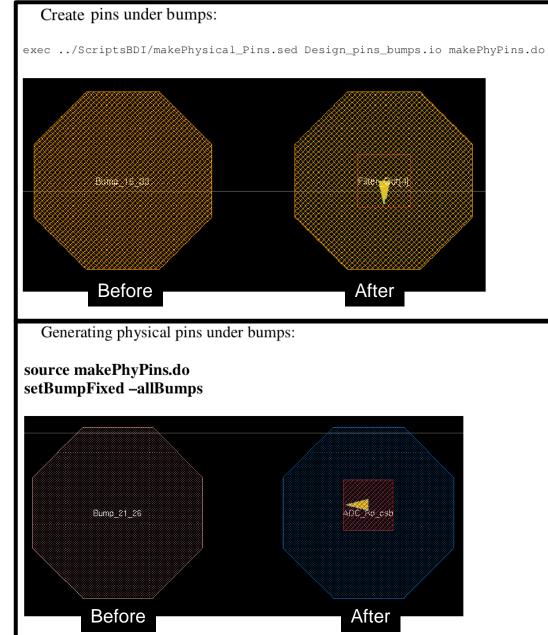

# **Custom Scripts Enabling Routing on DBIs**

Placing logical pins on bumps (DBIs), and extract their location.

Generating Physical pins from these locations.

They can now be used as terminals for routing.

# Automatic P & R Design Flow (From Floor-Plan to Routed Design)

- DBIs Placement

- TSVs Placement

- Obstructions on TSVs

- Clock routing

- Final routing

#### A The M6 layer must not be used during routing. This layer is reserved for DBI.

Routing Clock Nets

#### Route > NanoRoute > Route...

Switch Selected Nets Only in the *Routing Control* panel.

In the **Attribute** Menu, select : Net Type : **Clock Nets** Avoid Detour: **True** (this allows to route the clock nets as straight as possible)

Use the "Mode setup" panel to switch the different options (for example, define the bottom/top routing layer).

Click OK to run Nanoroute.

|                                  | NanoRoute                                        |                                    |

|----------------------------------|--------------------------------------------------|------------------------------------|

| Routing Phase                    |                                                  |                                    |

| <ul> <li>Global Route</li> </ul> |                                                  |                                    |

| <ul> <li>Detail Route</li> </ul> | Start teration 0 End teration defau              | uit                                |

| est Route Optimization           | Optimize Via 🔄 Optimize Wire                     |                                    |

| Concurrent Routing Feat          | ures                                             | 1                                  |

| <ul> <li>Fix Antenna</li> </ul>  | insert Diodes Diode Cell Name                    |                                    |

|                                  | Congestion Timing                                |                                    |

| _ Tining Driven                  | Effort 5                                         | SMART.                             |

| _ SIDriven                       |                                                  |                                    |

| Post Route SI                    | St Victor F14                                    | <u>e</u>                           |

| 🔄 Lithe Driven                   |                                                  |                                    |

| _ Post Route Litho Repa          | ir                                               |                                    |

| Routing Control                  |                                                  |                                    |

| Selected Nets Only               | Bottom Layer 1 Top Layer 5                       |                                    |

| LI ECO Route                     | annue rober 1 Let and a D                        |                                    |

| Area Route                       | Ārea                                             | Pal Select Area and Route          |

| a meanion                        | 111.00                                           |                                    |

| Job Control                      |                                                  |                                    |

| <ul> <li>Auto Stop</li> </ul>    |                                                  |                                    |

| lumber of Thread(s) For M        | ultiple Threadact 1 NanoBoute/4                  | Attributes –                       |

| Number of Thread(s) Fo           |                                                  |                                    |

| Number of Host(s) Fo             | r Super                                          |                                    |

| Set Multiple CPU.                | 🔹 N=1 ype(s): 📕 Clorik Nets 🔄 External Vers      | 🔲 Cirthibal Nets 🔛 Stellandeb Nets |

|                                  | 🐳 Net Name(C):                                   |                                    |

| QK Apply                         | D. C.                                            |                                    |

|                                  | Skip Antenna - ↓ TRUE ↓ FALSE ♦ ASIS Tup Lay     | ASIS Bullom Layer ASIS             |

|                                  | Skip Routing 👃 i KUE 🧅 -ALSE 🔶 AS S - Wolght     | ASIS Scooling ASIS                 |

|                                  | Avoid Detour 🔹 INUE 💠 -ALSE 🕹 ASIS – Shield N    |                                    |

|                                  |                                                  |                                    |

|                                  | 5 Frevention 🐟 IRUE 🗢 -ALSE 🕈 AS S - Noncefiz    | cult Rule ASIS                     |

|                                  | S Fost Foute Fix 💠 TRUE 💠 FALSE 🔶 AS S 🛛 Pattern | Asis 🛨                             |

|                                  |                                                  |                                    |

|                                  |                                                  | ≡lec:                              |

|                                  | 20 20 20                                         | <u>Teb</u>                         |

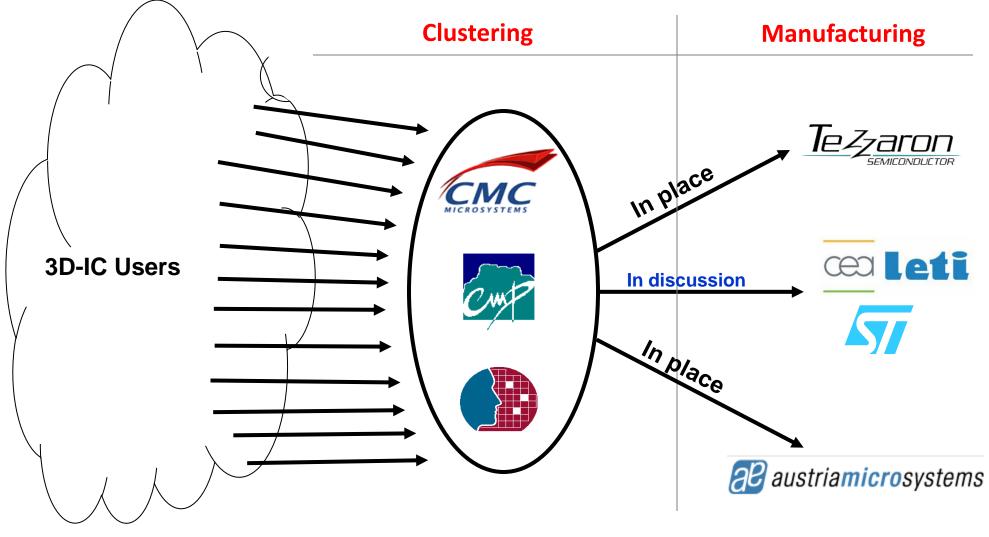

CMC, CMP, MOSIS already cooperating since several years offering commonly some processes, and sharing the manufacturing prices. They are engaged this time with the 3D-IC process offer.

A very collaborative work has been achieved and still ongoing between the parties CMC, CMP, MOSIS, FermiLab, Tezzaron, HEP Labs, NCSU.

A Unique and Unprecedented Design Platform resulted from the collaboration. (Industrial CAD vendors just starting addressing the features)

First CMC/CMP/MOSIS MPW run planned for March 2011.

Other 3D-IC processes are explored :

- CMP is in discussion with Austriamicrosystems for a TSV process for System-in-Package (SiP) applications.

- CMP is in discussion with LETI / ST for the access to a 3D-IC process using Cu TSV.