Topical Workshop on Electronics for Particle Physics 2010 — Aachen, Germany, 20-24 September 2010

#### http://pmm2.in2p3.fr

E. Wanlin on behalf of the PMm<sup>2</sup> collaboration

# A R&D on a triggerless acquisition for next generation neutrino experiments

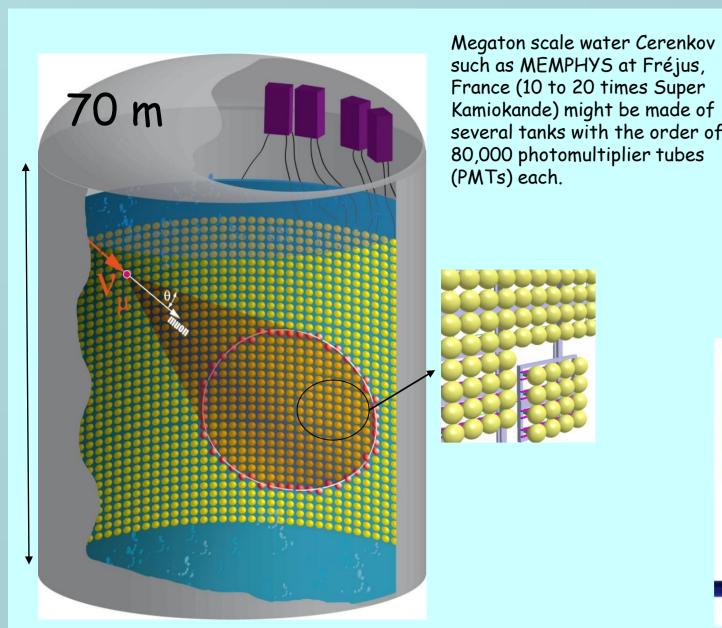

The next generation of megaton scale water tanks implies very large surfaces of photodetection and a large volume of data. PMm<sup>2</sup> is a funded R&D project to implement and propose a demonstrator. The main features are:

Replace large 20" PMTs by 12" Modular design of 16 PMTs arrays Underwater front-end electronics Surface controller Triggerless data acquisition Demonstrator with 16 8" PMTs

#### **Global Architecture and Constraints**

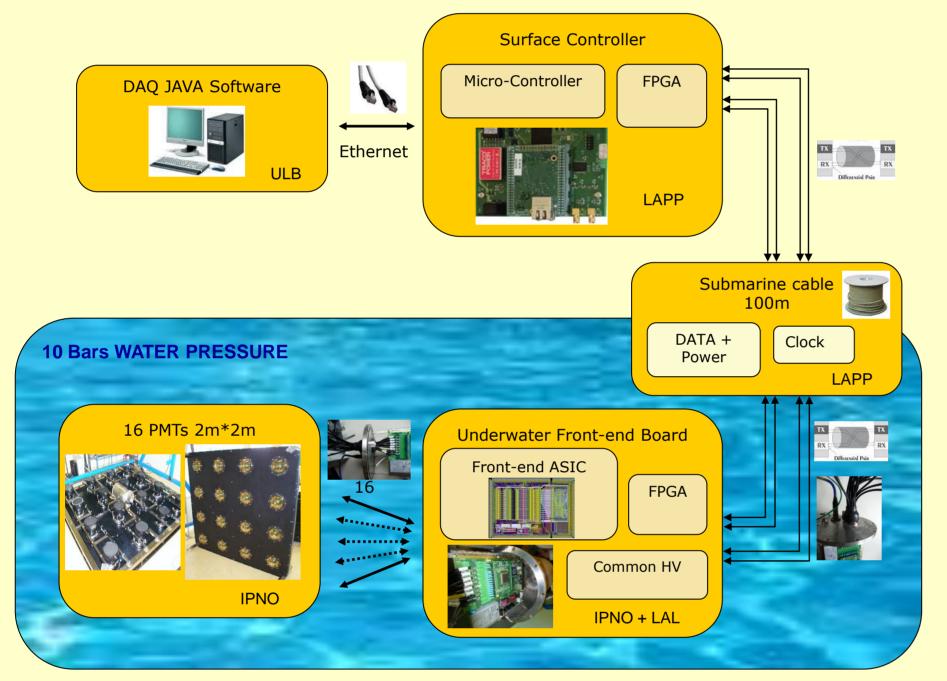

#### **Underwater Front-End**

- Modular design of 16 PMTs arrays, 2 m x 2 m

Low cost

- Single high voltage power supply for 16 PMTs

- Gain compensation on front-end electronics

- Triggerless

- 5 kHz noise pulses rate of PMTs

- 10-bar pressure/water resistance

- PMTs data transferred continuously to the surface controller

- Coincidence and data analysis off line

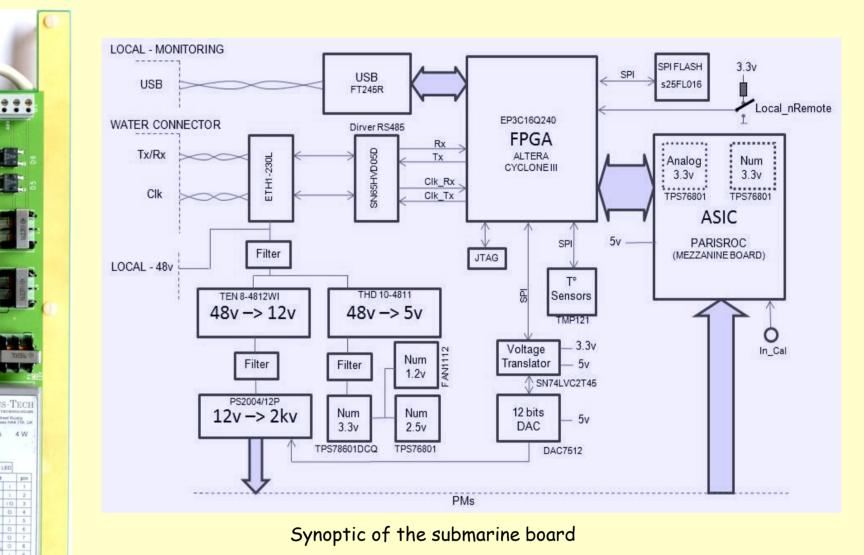

- Analog front-end ASIC PARISROC (see below)

- Altera Cyclone3 FPGA for slow-control and readout of the ASIC and data transmission from/towards the surface controller (mean 5 Mbps)

- Single tunable (up to 2 kV) High Voltage via a 12-bit DAC

- Surface monitoring of temperature

- USB interface for standalone debugging

- DC/DC converters for 48 V / 12 V, 48 V / 5 V and linear regulators

- PCB (8 layers, class 5) design meets rules of isolation, filtering, cooling and EMC

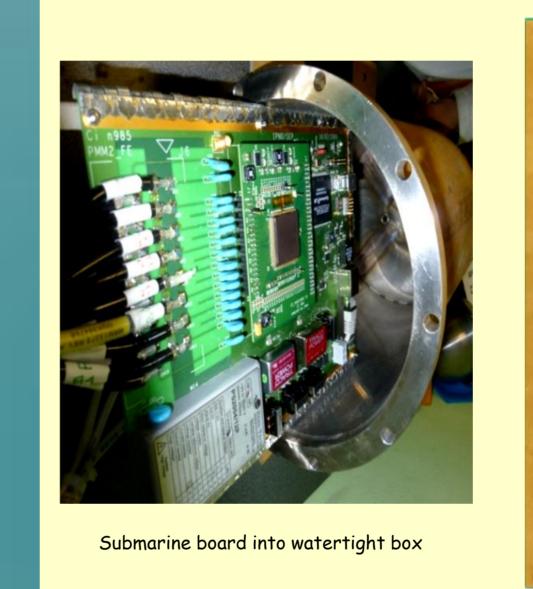

- Watertight box, connectors and PMTs' bases potting tested up to 13 bars

Global synoptic of PMm<sup>2</sup>

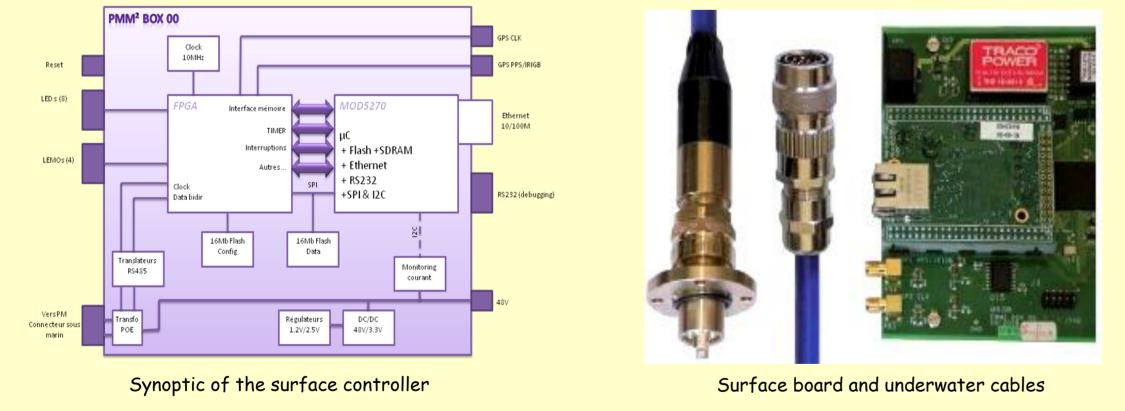

#### Surface Controller, 100m Cable

- Micro-Controller for connection to Ethernet network

- FPGA for synchronization and dialogue with submarine board

- 100m cable, cat.5 class D, with 2 differential pairs:

- 10 MHz GPS clock for synchronization

- dataflow + Power Over Éthernet 48 V / 30 W

- Dedicated serial Manchester protocol (RS485 levels) 5 Mbps

- Underwater harness: industrial electrical and pressure tests

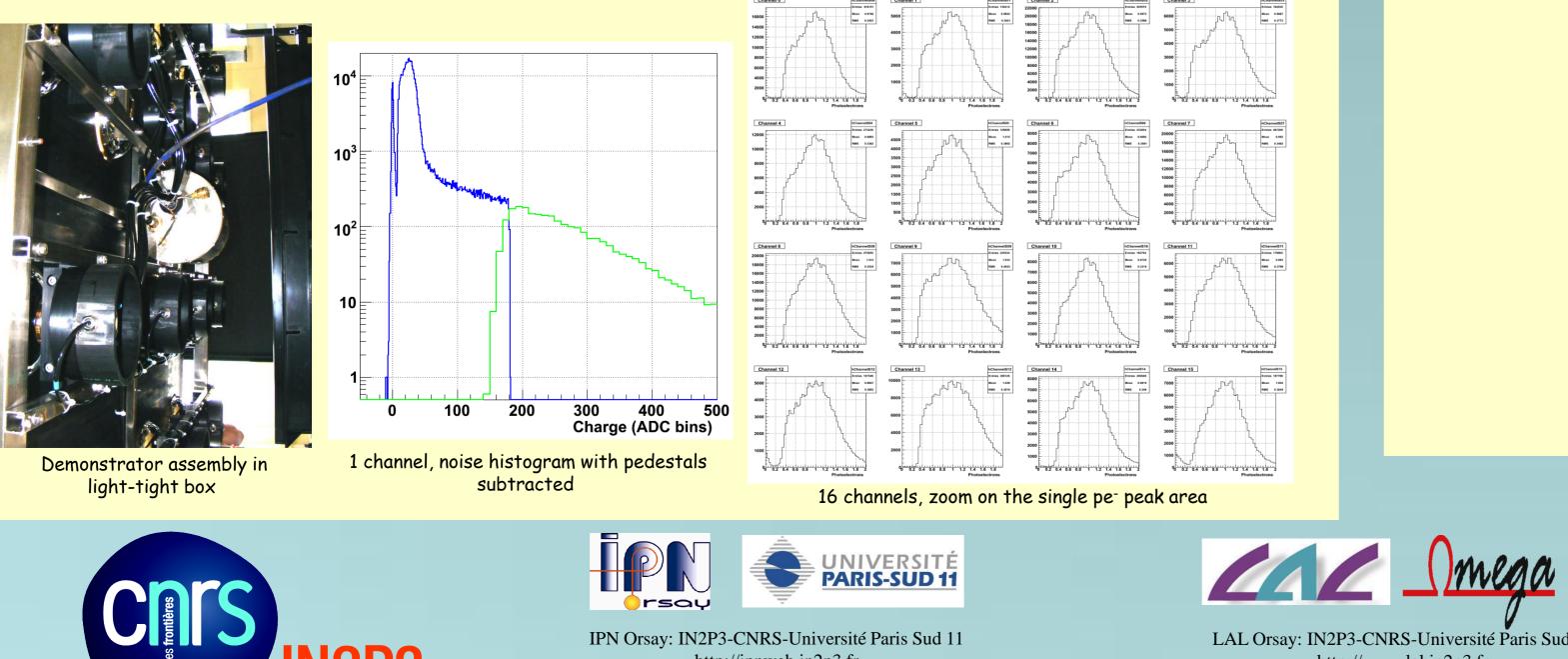

## 16 8" PMTs Demonstrator: First Results

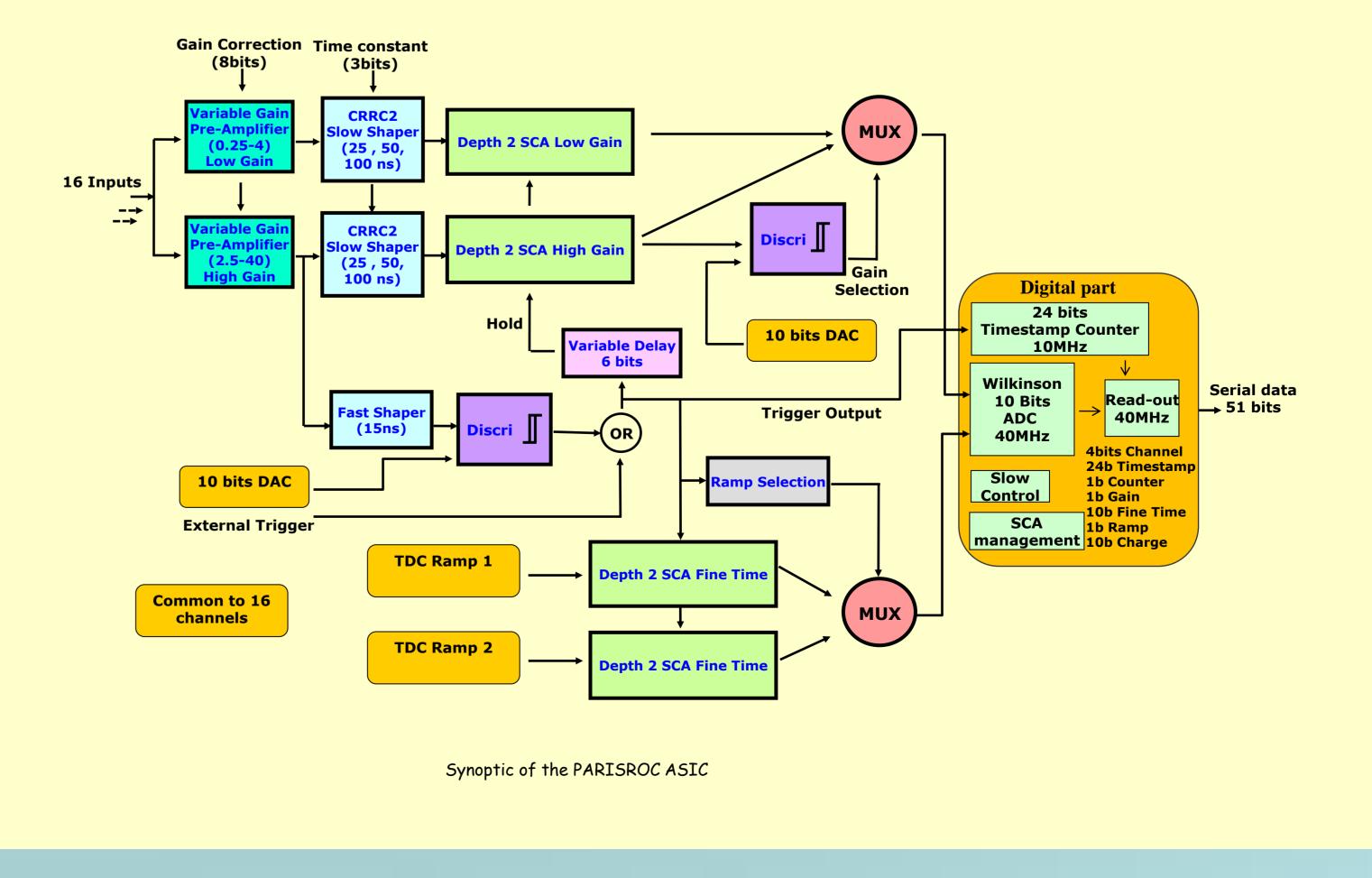

### Front-End ASIC (PARISROC)

- AMS SiGe 0.35 µm

- 16 independent channels

- Independent gain adjustment by channel

- Charge and time digitization

- Charge: 0 to 300x10<sup>6</sup> electrons

- efficiency from 10<sup>6</sup> electrons input charge

- Time resolution 425 ps RMS

- 24-bit timestamp counter @ 10 MHz

- Virtual 12-bit ADC @ 40 MHz

- (10-bit Wilkinson ADC + 2 gains with automatic selection)

- Serial readout @ 40 MHz

- Max conversion + readout time =  $45 \mu s$

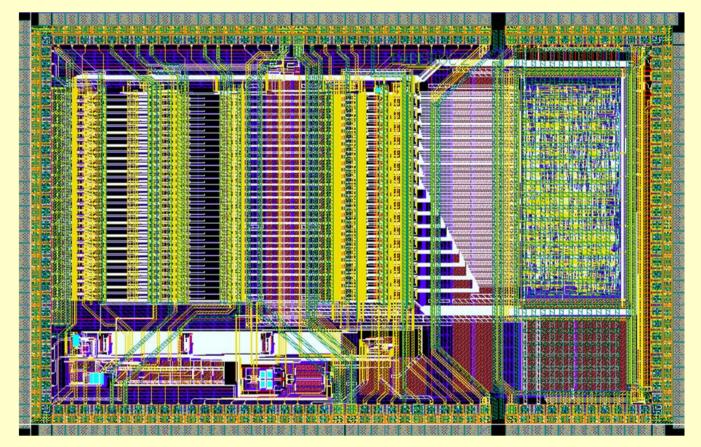

PARISROC Chip - 0.35  $\mu$ m SiGe - 5 mm x 3.4 mm

Charge measurement of PMTs and gain compensation

Ability of PARISROC to sustain the PMTs counting rate

Single photoelectron response with 0.3 pe<sup>-</sup> threshold, 1550 V

es deux infinis

LAPP Annecy: IN2P3-CNRS-Université de Haute Savoie http://lappweb.in2p3.fr D. Duchesneau, N. Dumont-Dayot, J. Favier, R. Hermel, J. Tassan-Viol, A. Zghiche

Université Libre de Bruxelles http://www.ulb.ac.be K. Hanson

http://ipnweb.in2p3.fr S. Drouet, B. Genolini, B.Y. Ky, T. Nguyen Trung, J. Peyré, J. Pouthas, P. Rosier, E.Wanlin LAL Orsay: IN2P3-CNRS-Université Paris Sud 11 http://www.lal.in2p3.fr J.-E. Campagne, S. Conforti, F. Dulucq, C. de La Taille, M. El Berni, G. Martin-Chassard