H.-G. Moser Max-Planck-Institut für Physik

### **Fast Pixel Detectors**

**CLIC** requirements

resolution: pitch: 10 μm (binary) 25 μm (analogue) occupancy: (3 cm) frame readout: 10 μm pitch or

25ns time resolution for 25µm pitch

1

power: 100 mW/cm<sup>2</sup> duty cycle: 150 ns on every 20ms even for 100µs readout time: 1:200 => 20W/cm<sup>2</sup> with power cycling

pattern recognition time stamp: 25ns

material: <100µm Si

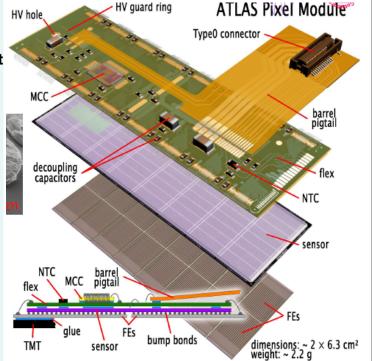

### State of the art: hybrid pixels

H.-G. Moser Max-Planck-Institut für Physik

CLIC09

**CERN**

15. Oct 09

$\Delta p \Delta q \ge 2 t$

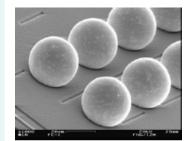

#### Face to face interconnection: ASIC - Sensor

HV guard ring

#### Definitely not low mass!

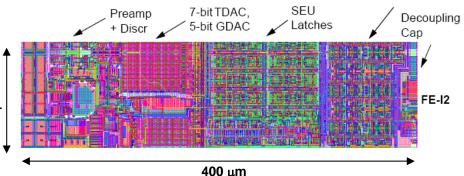

Granularity (resolution, occupancy) bump bonding limits pitch to O(50 µm) Pixel area 10000 µm<sup>2</sup> (CMOS 0.25µm) 50x400 µm<sup>2</sup> **Readout speed:** 25ns BX identification complex processing (pipeline) **Thickness** Thick! (250 µm Sensor + ASIC + interconnect) large signal needed! 200 mW/cm<sup>2</sup> (liquid cooling) Power Fill factor (low mass) 71% (ATLAS) Add functionalities (calibration, 0suppression, clustering) ok, especially going to even smaller **DSM Radiation hardness** Yes (till  $10^{15}$  n/cm<sup>2</sup>)

### **Monolithic Detectors**

Integrate readout electronics (amplification) into sensor

H.-G. Moser Max-Planck-Institut für Physik no interconnection low mass

Examples:

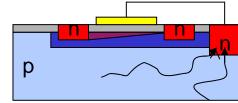

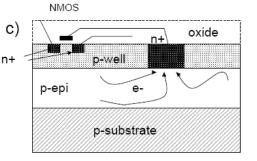

CMOS sensors (MAPS) 'standard CMOS' process use un-depleted epi layer as sensor complex CMOS circuit (limited to NMOS) small signal, slow charge collection

DEPFET

depleted bulk fast, large signal limited signal processing

Fairly different detector architectures In common:

low mass => ideal for high precision detectors slower than hybrid pixels moderate radiation hardness (ok for e\*e-, not for pp)

## **CMOS Sensors**

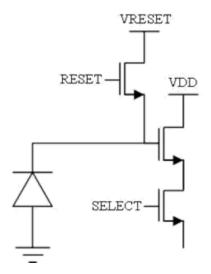

Charge collection by diffusion (in un-depleted epi layer) CMOS readout electronic integrated. Small signal, yet S/N > 20)

H.-G<mark>. Moser</mark> Max-Planck-Institut für Physik

> CLIC09 CERN 15. Oct 09

$\Delta p \cdot \Delta q \ge \frac{1}{2} t$

Performance limited by NMOS Use only:

slow, no complex processing

Granularity (resolution, occupancy) 10 µm pitch (MIMOSA18) Readout speed (complex processing) slow charge collection by diffusion frame readout (100 µs) Thickness <100µm (small signal anyway) Power low (depends on speed and complexity) Fill factor (low mass) low (periphery), tiling, stitching Add functionalities (calibration, 0-suppression, clustering) difficult (only NMOS transistors)

4

H.-G. Moser Max-Planck-Institut für Physik

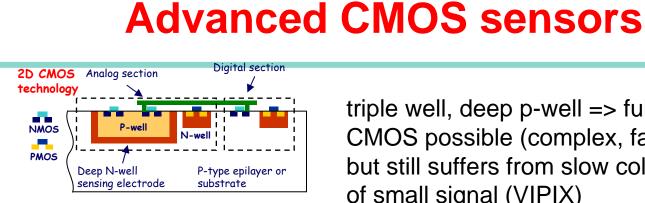

triple well, deep p-well => full CMOS possible (complex, fast) but still suffers from slow collection of small signal (VIPIX)

High resistivity epi (IPHC) using XFAB-0.6 PIN process 1 k $\Omega$ cm -> ~ 14 µm depleted Charge collection within 5 ns

INMAPS (RAL): deep p-well shields PMOS completely High resistivity substrate (1-10 k $\Omega$ cm) 10-20 µm depleted Charge collection within 5 ns

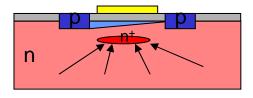

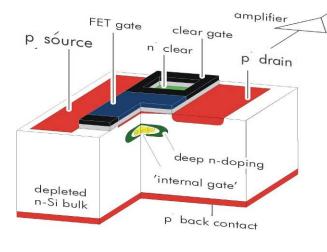

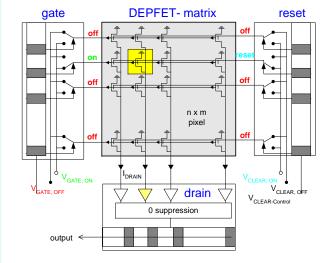

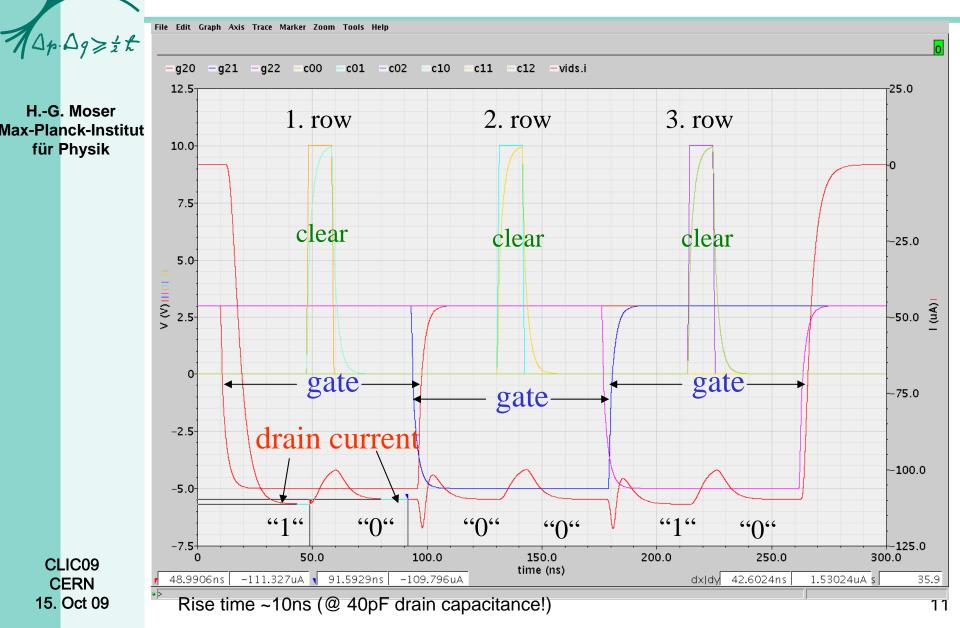

#### DEPFET

H.-G<mark>. Moser</mark> Max-Planck-Institut für Physik

#### FET on fully depleted silicon Baseline for Belle II PXD

Granularity (resolution, occupancy) 20µm pitch ok Readout speed slow: frame readout O(10 µs) Thickness 50µm, with good S/N Power <100mW/cm² (rolling shutter) Fill factor high: monolithic wafer scale se

high: monolithic wafer scale sensors Add functionalities (calibration, 0-suppression, clustering)

No (only in readout ASIC) Radiation hardness ok to 10 Mrad

H.-G. Moser Max-Planck-Institut für Physik

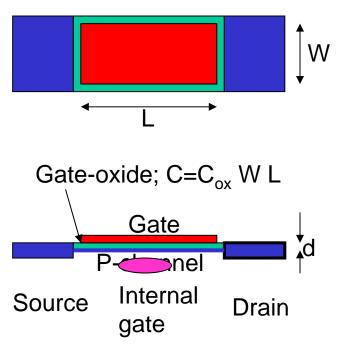

#### How does it work?

A charge q in the internal gate influences a mirror charge  $\alpha$ q in the channel ( $\alpha$  <1, for stray capacitance) This mirror charge is compensated by a change of the gate voltage:

CLIC09 CERN 15. Oct 09

$$\Delta V = \alpha q / C = \alpha q / (C_{ox} W L)$$

FET in saturation:

$$I_{d} = \frac{W}{2^{d}L} \neq u \underbrace{W}_{2L} \left( u G_{ox} + \underbrace{(v G_{ox} q_{s} V_{th})}_{C_{ox}} v_{th} \right)^{2}$$

$I_{d}: source-drain current$  $C_{ox}; sheet capacitance of gate oxide$  $\mu: mobility (p-channel: holes)$  $V_{g}: gate voltage$  $V_{th}: threshold voltage$

Cramsersion taetore:

$$g_{m} = \frac{dI_{d}}{dI_{d}} \underbrace{\frac{W}{\partial H_{d}}}_{dq_{s}} \underbrace{\frac{W}{\partial \mu}}_{L^{2}} \underbrace{\mu C_{ox}}_{V_{G}} \underbrace{W_{G}}_{V_{G}} \underbrace{-V_{th}}_{C_{ox}WL} \underbrace{-V_{th}}_{V_{th}} = \alpha \sqrt{2 \frac{I_{d}\mu}{L^{3}WC_{ox}}}$$

$$g_{g_q^n} \equiv \sqrt{2 \frac{W_{\mu}C_{ox}I_d}{W_{LC_{ox}}}} = \alpha \frac{g_m}{C}$$

7

### **Intrinsic Noise**

Using:

$$g_q = \alpha \frac{g_m}{C}$$

$\left\langle ENC^2 \right\rangle = \frac{e^2}{3q^2} kT \frac{g_m}{\left(\alpha \frac{g_m}{C}\right)^2} \frac{1}{\tau} = \frac{\alpha^2}{3q^2} kT \frac{e^2}{g_m} \frac{C^2}{\tau}$

H.-G. Moser Max-Planck-Institut für Physik

p. △9≥źt

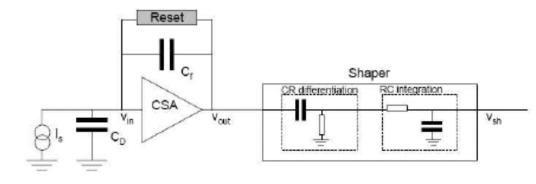

A similar expression can be deduced for a diode and charge sensitive amplifier (CSA):

$$\langle ENC^2 \rangle = \frac{1}{3} kT \frac{C_t^2}{g_m} \frac{e^2}{q^2 \tau}$$

However, with  $C_t$ : total capacitance ( $C_D+C_f+...$ ) (and  $\alpha = 1$ , of course)

CLIC09 CERN 15. Oct 09 Achieved: 40e noise at a BW of 50MHz (S/N 100:1 for a 50µm sensor) However: usually noise dominated by external components

#### **Test Beam**

|                   | Module 0     | Module 1    | Module 2      | Module 3     | Module 4     | Module 5    |

|-------------------|--------------|-------------|---------------|--------------|--------------|-------------|

| TB 2008           | CCGME-S90K02 | CCGME-90K02 | SIMCME-S90K00 | CCGME-S90103 | CCGME-S90100 | CCGME-90100 |

|                   | 32x24 μm     | 32x24 µm    | 32x24 µm      | 24x24 μm     | 32x24 µm     | 32x24 µm    |

| X residual [μm]   | 2.9          | 2.2         | 2.3           | 2.0          | 3.1          | 3.4         |

| Y residual [μm]   | 2.3          | 1.7         | 1.7           | 1.7          | 2.2          | 2.6         |

| X resolution [µm] | 2.1          | 1.6         | 1.9           | 1.3          | 2.6          | 2.4         |

| Y resolution [µm] | 1.5          | 1.3         | 1.2           | 1.2          | 1.8          | 1.7         |

Check performance of different designs

| 32x24 µm²: | L=6 µm W=20µm:  | g <sub>a</sub> = 360 pA/e |

|------------|-----------------|---------------------------|

| 20x20 µm²: | L=5 µm W=10µm:: | g <sub>a</sub> = 650 pA/e |

Results are for 'ILC'-like pixels (small pitch) and thick detectors Comparison and tuning of MC simulations => performance at Belle II

### **DEPFET Projects**

IXO wide f readout) DSSC x-ra single pix

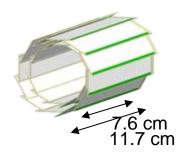

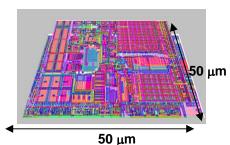

ILC vertex detector: 25x25  $\mu m^2$  pixels, 20  $\mu s$  frame readout, 50  $\mu m$  thick

# Belle II vertex detector: 50x75 µm<sup>2</sup> pixels, 10(20)µs frame readout, 50µm thick

IXO wide field imager (X-ray detector, frame readout)

DSSC x-ray imager for XFEL: 200x200µm pitch, single pixel readout, 200ns time resolution Bump bonded hybrid technology

> Min, size given by Aluminum pitch (8µm) Smallest cell operated up to now: 20x20µm<sup>2</sup> 128x128 matrix worked well in TB09

Smaller pixels need improved process technology (plasma etch)

10

H.-G. Moser Max-Planck-Institut für Physik

$\Delta p \Delta q \ge \frac{1}{2} t$

## **Intrinsic Speed**

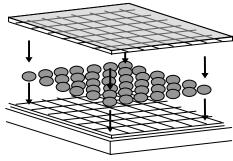

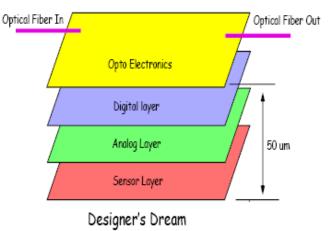

## **3D Interconnection**

$\Delta_p \Delta_q \ge \frac{1}{2} \mathcal{L}$  Basic Problem:

#### How to integrate good sensors and good electronic circuits?

H.-G. Moser Max-Planck-Institut für Physik

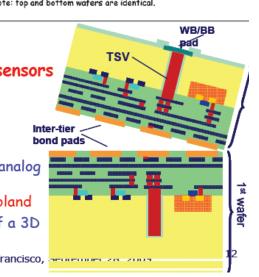

3D Interconnection:

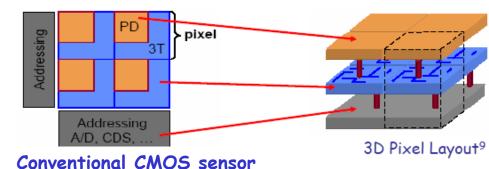

Two or more layers (="tiers") of thinned semiconductor de "monolithic" circuit.

Different layers can be made in different technology (high ohmic, BiCMOS, deep sub-µ CMOS, Si

3D is driven by industry:

- Reduces R,L and C.

- Improves speed.

- Reduces interconnect power, x-talk.

- Reduces chip size.

- Each layer can be optimized individually.

Si pixel sensor

**BiCMOS** analogue

Analog IC

Digital IC

CMOS digital

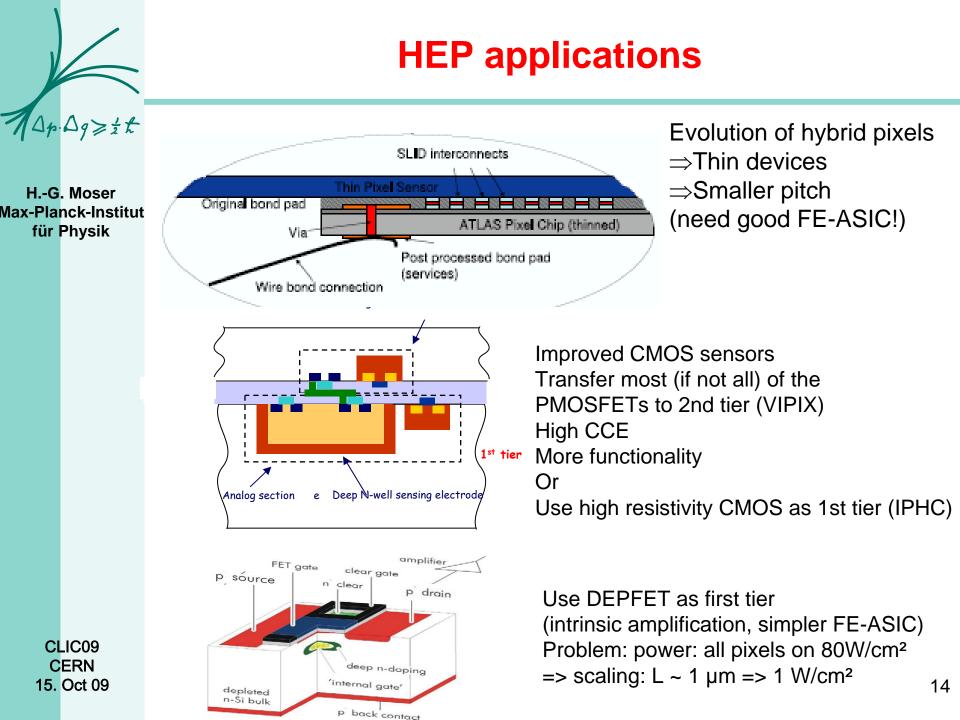

## **Advantages of 3D for HEP detectors**

Multilayer electronics:

Max-Planck-Institut für Physik Split analogue and digital part Use different, individually optimized technologies:

-> gain in performance, power,

speed, rad-hardness, complexity.

-> smaller area (reduce pixel size or more functionality).

4-side abuttable devices:

-> no dead space.

- -> simpler module layout.

- -> larger modules.

(reduce complexity and material)

(optical, similar: MAPS)

50 x 400 μm<sup>2</sup> (0.25 μm) May shrink to ~ 50 x 50 μm<sup>2</sup> (130 nm)

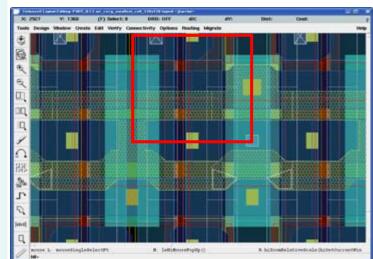

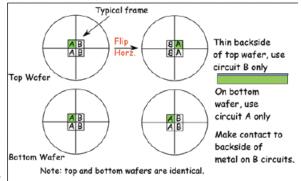

### **Fermilab 3D-IC**

H.-G<mark>. Moser</mark> Max-Planck-Institut für Physik

$\Delta p \cdot \Delta g \ge \frac{1}{2} t$

#### First 3D-IC Tezzaron Multiproject Run

Broad range of architectures and applications:

#### MAPS

Convert 2D MAPS device to a full CMOS 3D design, with digital readout separated from the sensor and the analog front-end – Italy, France

#### Readout chips for high resistivity pixel sensors

- Convert MIT LL 3D SOI design to the Tezzaron/Chartered process - Fermilab

- Convert current 0.25 μm readout pixel electronics to a 3D structure with separate analog and digital tiers - France/US

- X-ray imaging/timing chip Fermilab/BNL/Poland

- 3D chip with structures to test feasibility of a 3D integrated stacked trigger layer.

Valerio Re - IEEE 3D-IC Conference, San Francisco, acticum

Consortium of about 15 institutions from US, France, Italy, Germany, Poland

# **Silicon Photomultiplier**

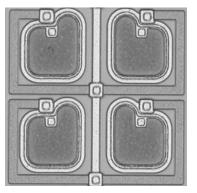

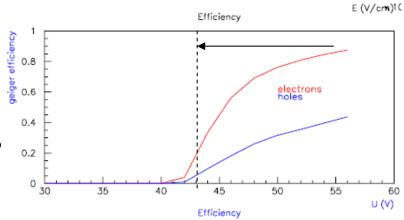

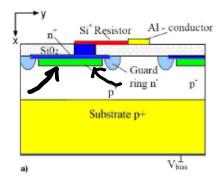

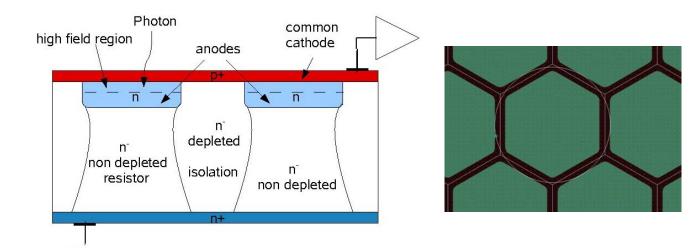

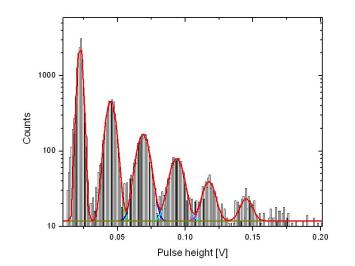

Al - conductor Si<sup>®</sup> Resistor  $\Delta_{p}$   $\Delta_{g} \ge \frac{1}{2} \mathcal{L}$  Basic building block: avalanche photodiode operating in Geiger mode ring n レンス:X 150 H.-G. Moser Substrate p+ Max-Planck-Institu für Physik V<sub>bias</sub> 10 [V/cm] Geiger region H10 -----Drift region  $10^{2}$ The device is operated above the breakdown voltage Photons are absorbed in depleted silicon, create e/h pairs b) x [µm] Avalanche amplification (Geiger breakdown) occurs Passive quenching by integrated resistor (limits current) The signal size ("amplification") is given by the overvoltage and the cell capacity  $Q = C \times \Delta U (\sim 10^6)$ binary signal of fixed size! SiPM @ 41.4 V an Different Intensities Array of cells all connected to a single output: Signal =  $\Sigma$  of cells simultaneously fired t of Ever CLIC09 **CERN** If probability to hit a single cell << 1 15. Oct 09 6 => Signal proportional to # photons

Peak Voltage (V)

H.-G. Moser Max-Planck-Institut für Physik

# Very good photon detector

- Simple, robust device

- Photon counting capability

- Easy calibration (counting)

- Insensitive to magnetic fields

- Fast response: < 1 ns (100ps demonstrated)</li>

- Large signal (only simple amplifier needed)

- Good quantum efficiency

- No damage by accidental light

- Cheap

- Low operation voltage (40 70 V)

- Many applications possible (replacement of PMTs)

- But: no position resolution within matrix

| Hamamatsu S10362                     |

|--------------------------------------|

| 1 x 1 mm²                            |

| 1600 pixel                           |

| Pixel size: ~25 x 25 μm <sup>2</sup> |

H.-G. Moser Max-Planck-Institut für Physik

CLIC09

**CERN**

15. Oct 09

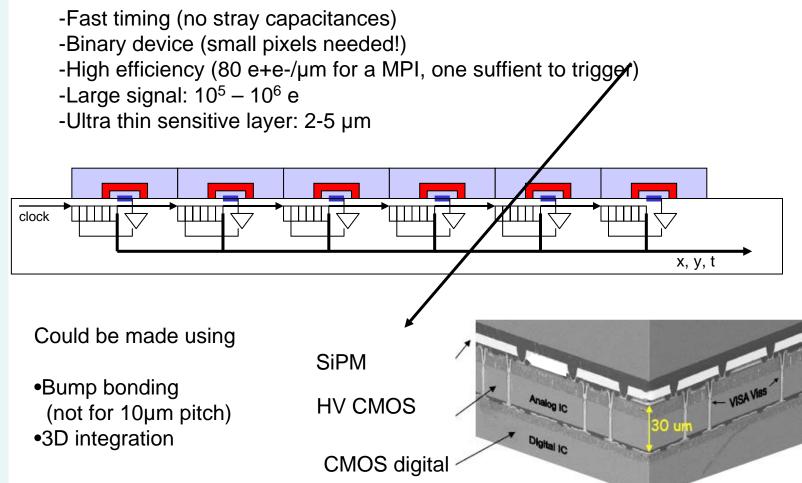

## **Smart SiPMs as tracker**

Connect ASIC chip to SiPM

For each pixel: signal detection & active quenching (optional)

### **Possible Problems**

#### Dark rate (noise occupancy)

~ 1 MHz/mm<sup>2</sup>

H.-G. Moser Max-Planck-Institut für Physik

CLIC09

CERN 15. Oct 09 Single pixel occupancy (10 x 10 µm<sup>2</sup> pixel, 150ns integration)

$\Rightarrow$ 1.5 x 10<sup>-5</sup> (with 25ns time resolution): 2.5 x 10<sup>-6</sup>

#### **Cross talk**

O(10%) in 1 mm<sup>2</sup>??

Reduce by operating at lower voltage MIP: 80 pairs/µm 10% single electron efficiency: >98% for a MIP

=>Lower dark rate =>Lower cross talk

#### Fill factor:

80% for large pixels (but including structures)drift region underneath HF may help

•double layer sensor?

19

### Conclusions

Fast Pixel Detectors:

H.-G. Moser Max-Planck-Institut für Physik

$p \Delta g \ge \frac{1}{2} t$

Hybrid Pixels (LHC-like): too much material, large pixels CMOS Sensors: too slow DEPFET: too slow (frame readout)

Advanced CMOS: very interesting. Key: PMOS & high resistivity epi

3D integration: solves many problems:

evolution/combination of hybrid pixels, MAPS or DEPFETs  $\Rightarrow$  Most promising way to go!

Avalanche arrays (SiPMs with single pixel readout) ultrafast timing (< 1 ns) possible needs 3D technology potential drawback: fill factor (dead areas)

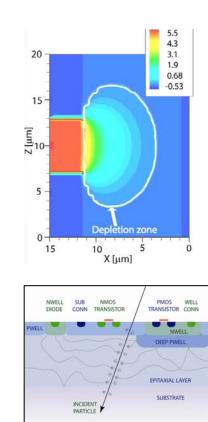

# SiMPL: Undepleted bulk as resistor

Shaping of electrical field (naturally du to implantation profile) Bulk under HF region remains un-depleted, acts as resistor Bulk in between HF region is depleted (isolates the pixels from each other)

$\Delta p \Delta g \ge \frac{1}{2} t$

H.-G. Moser

Max-Planck-Institut für Physik

> CLIC09 CERN 15. Oct 09

No structures needed (poly, Al) -> small pitch possible