# The SiPM-on-tile system of the CMS High Granularity Calorimeter Upgrade (HGCAL)

Antoine Laudrain (DESY) for the CMS HGCAL Collaboration

## The High-Granularity Calorimeter upgrade

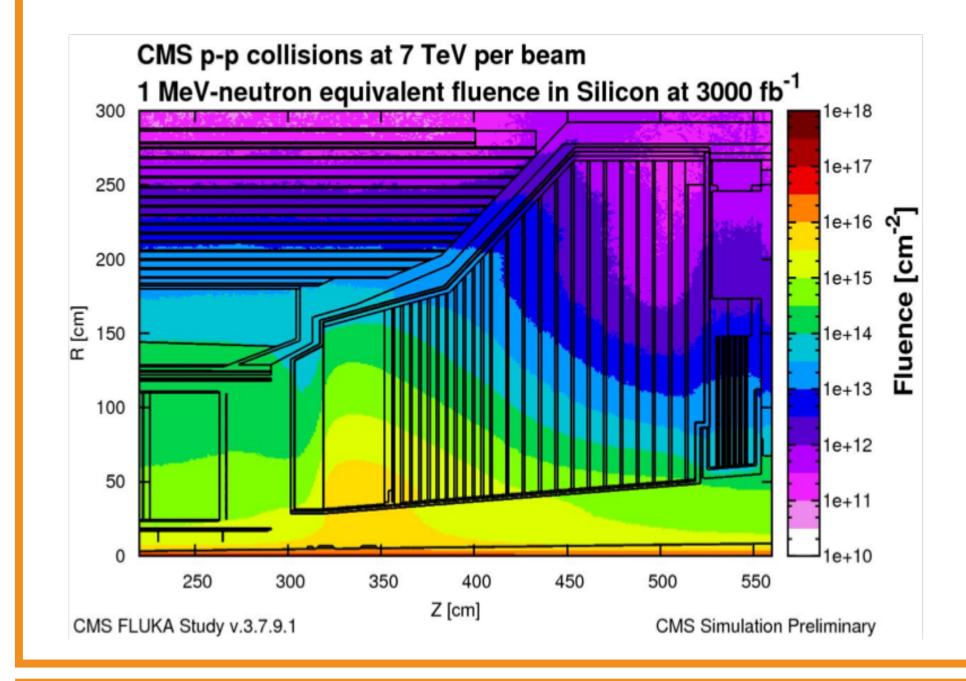

- High-Luminosity LHC to start in 2029 → increased pileup and radiation damage.

- $\rightarrow$  Need to replace the current endcap calorimeters  $\rightarrow$  5D (imaging) calorimeter using particle flow, operating at -30°C.

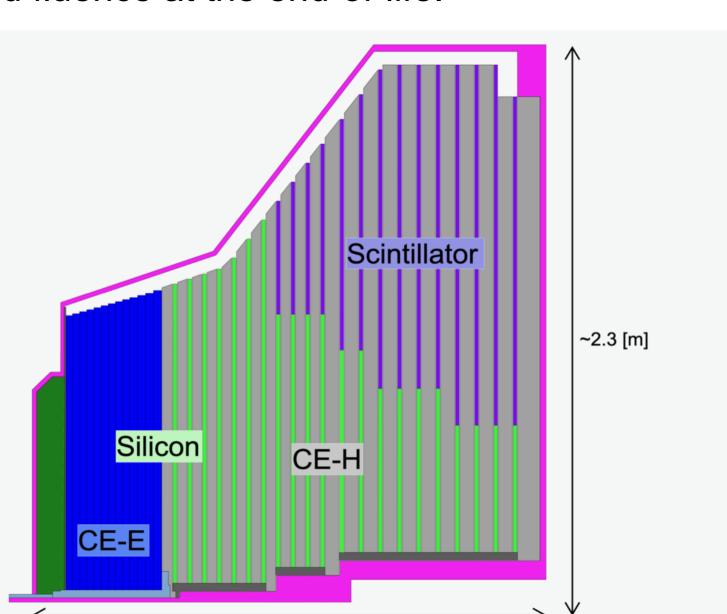

- Use both silicon sensors and SiPM-on-Tile technologies, depending on the expected fluence at the end-of-life.

#### Electromagnetic calorimeter (ECAL):

- 27.7X<sub>0</sub> or 1.5λ

- Cu / CuW / Pb absorbers

- Silicon **Hadronic calorimeter** (HCAL):

- 8.5λ

- steel absorbers

- Silicon detector section: where expected fluence at end of life > 5x10<sup>13</sup> n/cm<sup>2</sup>.

- Consists of hexagonal silicon sensors.

- Covers the ECAL and innermost part of the HCAL

- Cell size varies depending on its location in the calorimeter.

- More than 6M silicon sensors covering 620 m² area.

- Scintillator section: where expected fluence at end of life < 5x10<sup>13</sup> n/cm<sup>2</sup>.

- Consists of trapezoidal plastic scintillators tiles read out by silicon photomultipliers (SiPM-on-tiles technology).

- Covers the outermost part of the HCAL.

- Ensures S/N > 3 for minimum ionizing particles throughout the detector lifetime.

VTRX+

bidir e-links @ 80 Mbps

I2C, GPIO, ADC, DAC

uplinks @ 10.24 Gbps

ECON-T

e-link @ 1.28 Gbps

I2C, GPIO, ADC, DAC

ALDOV2

lpGBT (TX)

**HGCROC**

ECON-T

e-link @ 1.28 Gbps

Motherboard

@ 80 Mbps

Wingboard/

Cables

IpGBT (RX/TX)

**GBTSCA**

Tileboard PCB

downlink @ 2.56 Gbps

Fast Control (320 Mbps)

ECON-D

- Cell size increases radially from the beam line

- More than **240,000 SiPM-on-tiles** covering 370 m<sup>2</sup> area

#### The HGCAL SiPM-on-Tile section

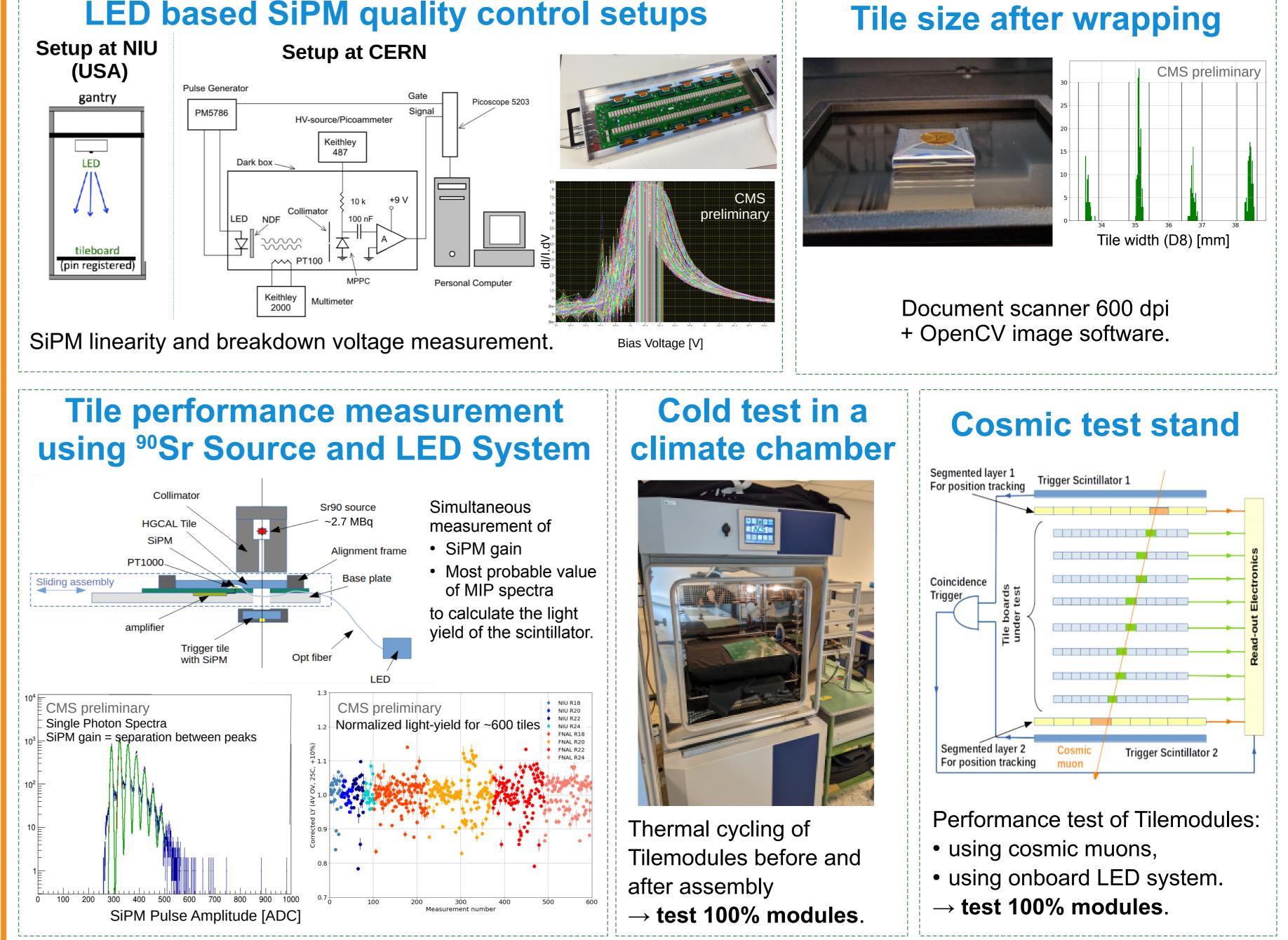

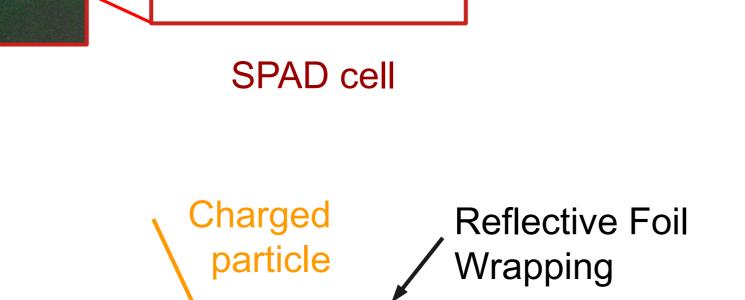

#### Sensors: the SiPM-on-Tile Technology

Individually wrapped plastic scintillator tiles, glued on the tileboard directly on top of SiPM.

1 SiPMs = thousands of single photon avalanche diodes (SPAD) working in Geiger mode.

Signal Amplification

And Digitization Digital Output Data

Scintillator

Tile

Analog

SiPM Signal

Tiles are plastic based, injection moulded or cast.

Mixed-Signal ASIC

- 21 scintillator tile sizes (23 mm to 55 mm side length).

- All SiPM: 9mm<sup>2</sup>.

- One low intensity LED for calibration next to each SiPM.

#### **HGCAL Tilemodules**

- The basic detector module in the SiPM-on-tile section:

- PCB,

- SiPMs + scintilators,

- HGCROC + front-end electronics.

- 8 main tilemodule types:

- Typically 64 channels / board, (up to 108),

- ~15x20 cm2 up to ~45x45 cm $^{2}$ ,

- ... with 35 variants.

## **Front-End Electronics**

#### • VTRx+:

Optically sends and receives signals from the back-end

#### • ECON-T:

- Receives trigger data from HGCROC

- Concentrates data and sends to LpGBT

## • ECON-D:

- Receives data from HGCROC

- Concentrates data and sends to LpGBT

## LpGBT:

- Transmits data to back-end via VTRx+

- Distributes clock, fast commands and configurations to the front-end electronics

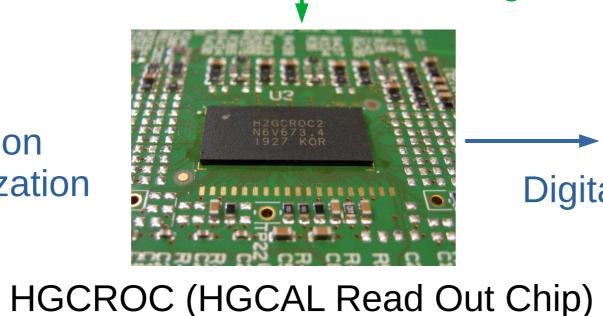

#### • HGCROC:

- Reads out the SiPM-on-tiles on the Tilemodule

- Up to 72 channels (1 or 2 per Tilemodule)

- GBT-SCA: Responsible for all slow control tasks on the Tilemodule

- ALDOV2: Voltage regulator chip for SiPMs on the Tilemodule

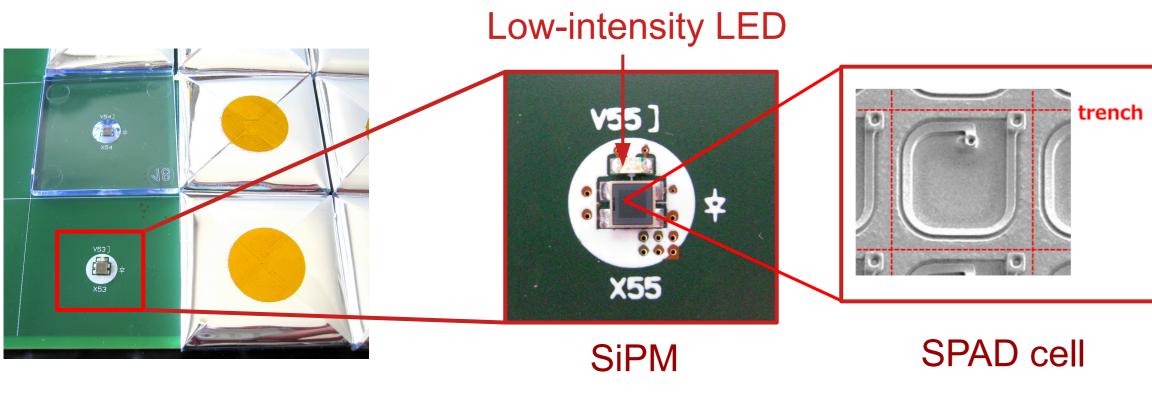

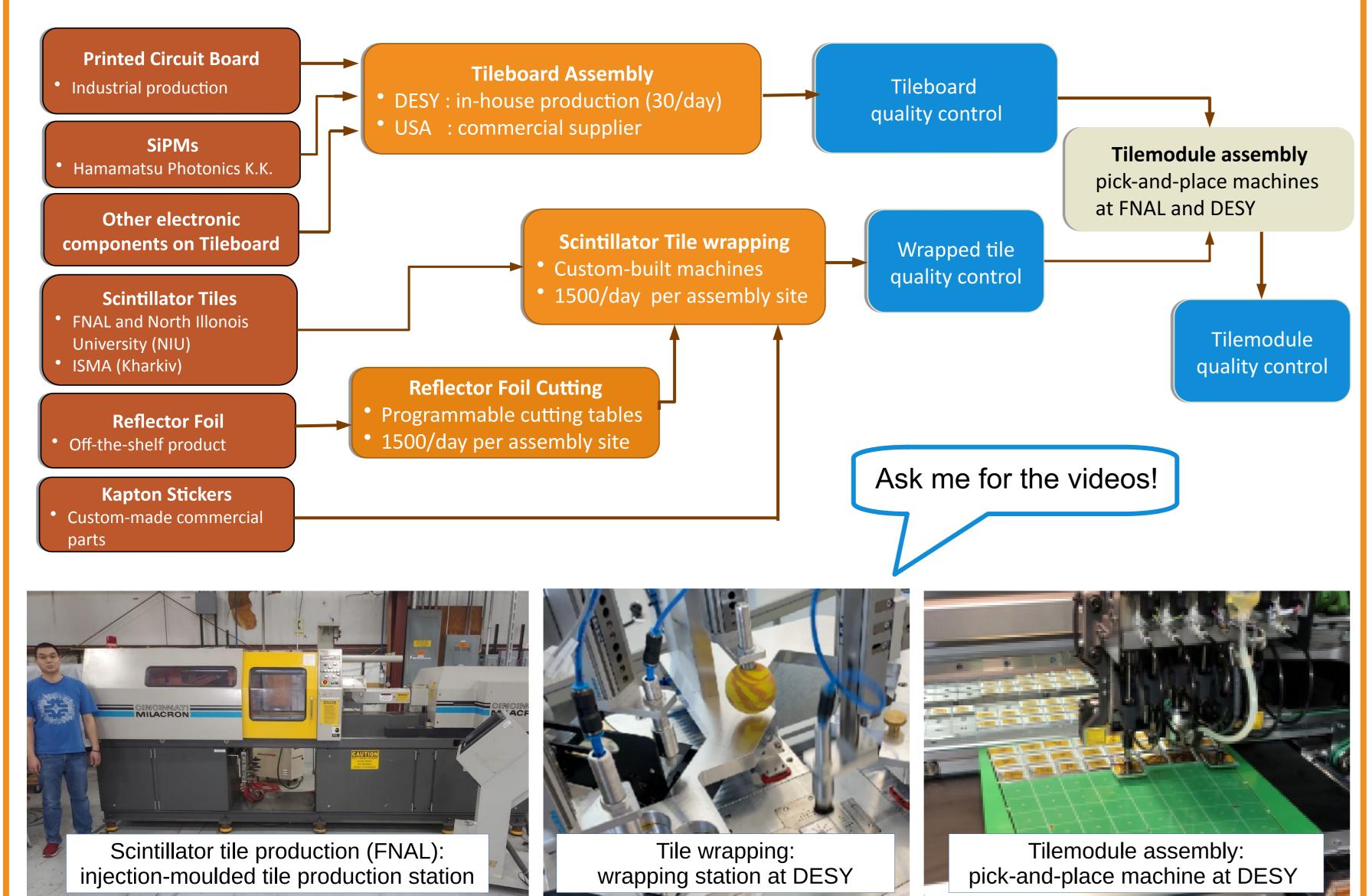

## Tilemodule production and assembly

- Tilemodule production for the final detector to begin this summer!

- Tilemodules will be produced and assembled at DESY (Hamburg, Germany) and Fermilab (USA).

#### **Quality Control**